# Annual Report 1994

F. J. Rammig B. Steinmüller Editors

Cadlab Report 11/95

# **Cadlab Annual Report**

# 1994

F. J. Rammig, B. Steinmüller (editors) compiled by: P. Hielscher

Cadlab Fürstenallee 7, D-33094 Paderborn, GERMANY

# Contents

| P | refac | ce      |             |                                                                                                                  | vii             |

|---|-------|---------|-------------|------------------------------------------------------------------------------------------------------------------|-----------------|

|   |       |         |             |                                                                                                                  |                 |

| T | 0     | vervie  | w           |                                                                                                                  | 100             |

| î | U     | ici vic |             |                                                                                                                  | 111             |

| 1 | Goa   | als and | Objectiv    | es                                                                                                               | 1               |

|   | 1.1   | Princi  | ipal Goals  | s                                                                                                                | 1               |

|   | 1.2   | Objec   | ctives of t | he Report Period                                                                                                 | 1               |

| 2 | Ore   | anizat  | ion         |                                                                                                                  | 2               |

| 4 | 2.1   |         |             |                                                                                                                  |                 |

|   | 2.2   |         |             | ·S                                                                                                               |                 |

|   | 2.2   | Doard   | i wiembei   |                                                                                                                  |                 |

| 3 | Sun   | imary   | of Progr    | ess                                                                                                              | 4               |

|   |       |         |             |                                                                                                                  |                 |

| п | Pr    | oject   | Group       | Reports                                                                                                          | 9               |

| 4 | Info  |         |             | ology - IT                                                                                                       | 9               |

|   | 4.1   |         |             | And the second |                 |

|   | 4.2   | Data    | Integratio  | n and Modelling - DIM                                                                                            | 10              |

|   |       | 4.2.1   | Baseline    | e                                                                                                                | 10              |

|   |       | 4.2.2   | Work de     | uring the Report Period                                                                                          | 10              |

|   |       |         | 4.2.2.1     | Database Federation Services                                                                                     | 10              |

|   |       |         | 4.2.2.2     | Federation of and Migration<br>Within Multiple Database Systems                                                  |                 |

|   |       |         | 4.2.2.3     | Schema-Evolution within Federated Sy                                                                             | vstems14        |

|   |       |         | 4.2.2.4     | STEP/EXPRESS Environment                                                                                         | 14              |

|   |       |         | 4.2.2.5     | Transaction Management in Design Er                                                                              | vironments16    |

|   |       |         | 4.2.2.6     | An Open Object-Oriented Integration I                                                                            | Environment17   |

|   |       |         | 4.2.2.7     | A Rule Meta Model for Active Databa                                                                              | se Systems17    |

|   |       |         | 4.2.2.8     | Semantics and Definition of Structural                                                                           | Defined Views18 |

|   | 4.3 | Proce  | ss and Sy  | stem Modelling - PSM                                                  | 19 |

|---|-----|--------|------------|-----------------------------------------------------------------------|----|

|   |     | 4.3.1  | Baseline   |                                                                       | 19 |

|   |     | 4.3.2  | Work du    | uring the Report Period                                               | 19 |

|   |     |        | 4.3.2.1    | Intelligent Framework Services (IFS)                                  | 20 |

|   |     |        | 4.3.2.2    | Pr/T-Net Modelling and Simulation Environment                         | 23 |

|   |     |        | 4.3.2.3    | System Modelling and Evaluation                                       | 25 |

|   |     |        | 4.3.2.4    | Hardware Design Methodologies                                         | 30 |

|   |     |        | 4.3.2.5    | System Design Under Timing Constraints                                | 32 |

|   |     |        | 4.3.2.6    | Evaluation of the JESSI Common Framework                              | 33 |

|   | 4.4 | Huma   | n-Compu    | iter Interaction - HCI                                                | 34 |

|   |     | 4.4.1  | Baseline   |                                                                       | 34 |

|   |     | 4.4.2  | Work du    | aring the Report Period                                               | 34 |

|   |     |        | 4.4.2.1    | Editor Object System (EOS)                                            | 34 |

|   |     |        | 4.4.2.2    | A Graphical Editor for Express-G (EXPREME)                            | 35 |

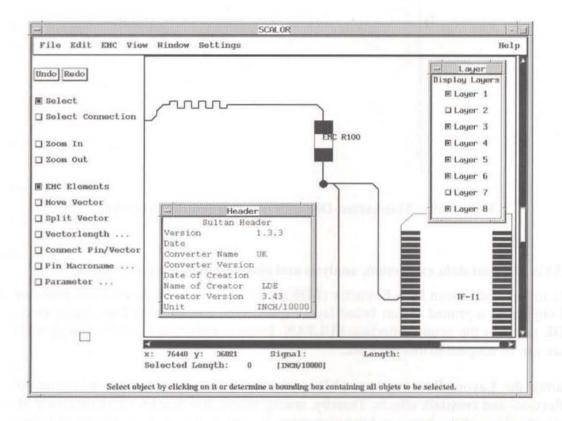

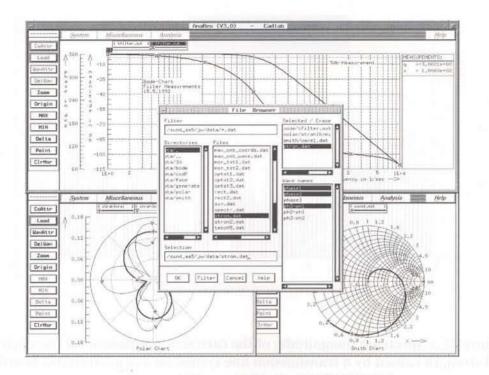

|   |     |        | 4.4.2.3    | A Graphical Editor for EMC-Workbench (SCALOR)                         | 36 |

|   |     |        | 4.4.2.4    | Visual Programming Environment                                        | 36 |

|   |     |        | 4.4.2.5    | EXPRESS/EXPRESS-P                                                     |    |

|   |     |        | 4.4.2.6    | VHDL'93                                                               | 37 |

|   |     |        | 4.4.2.7    | Other Activities                                                      | 37 |

|   | 4.5 | Sumn   | hary and ( | Outlook                                                               | 38 |

| 5 | Ana | log Sv | stem Eng   | gineering                                                             | 41 |

|   | 5.1 | 0.0    | -          | 4.0.1 Marchine survey of the survey of the survey of the              | 41 |

|   |     |        |            | 4.02 - Workshong the Koner frankl                                     | 41 |

|   | 5.3 |        | During th  | he Report Period                                                      | 43 |

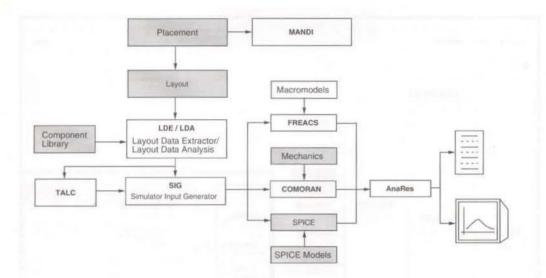

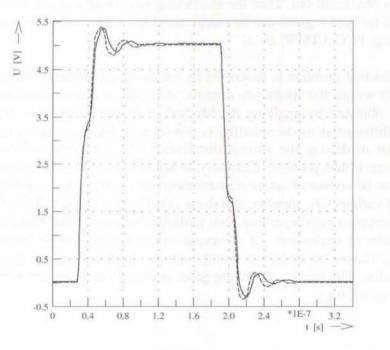

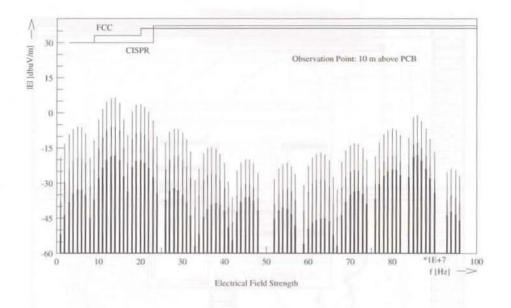

|   |     | 5.3.1  | EMC-W      | /orkbench                                                             | 44 |

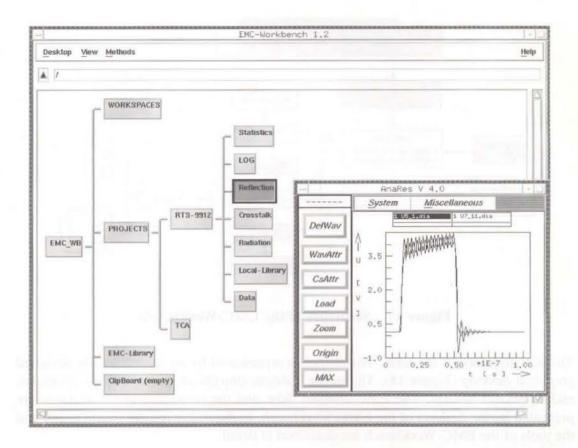

|   |     |        | 5.3.1.1    | Functionality and Structure                                           | 44 |

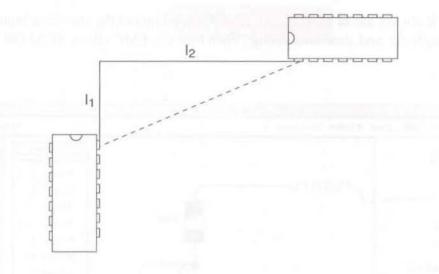

|   |     |        | 5.3.1.2    | Perennials of placement data considering EMC-aspects                  |    |

|   |     |        | 5.3.1.3    | Layout data extraction, analysis and generation<br>of simulator input |    |

|   |     |        | 5.3.1.4    | SCALOR - Schematic and Layout Editor                                  |    |

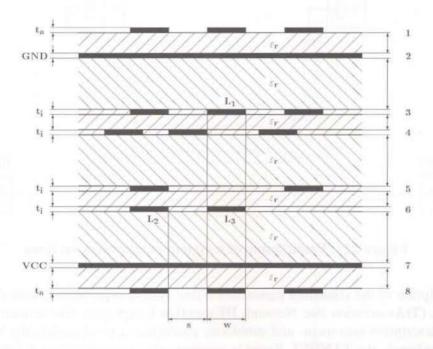

|   |     |        | 5.3.1.5    | Calculation of transmission line parameters                           |    |

|   |     |        | 5.3.1.6    | Simulation of reflection and crosstalk effects                        |    |

|   |     |        | 5.3.1.7    | Macromodel-Library                                                    |    |

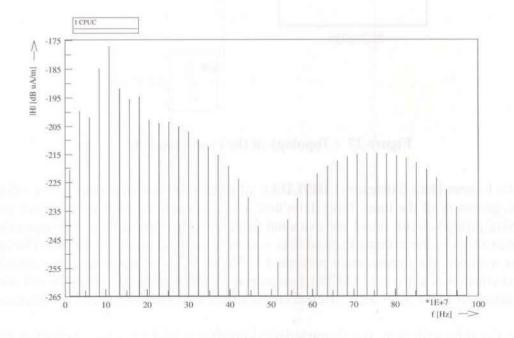

|   |     |        | 5.3.1.8             | Simulation and analysis of radiation and irradiation effects52                               |

|---|-----|--------|---------------------|----------------------------------------------------------------------------------------------|

|   |     |        | 5.3.1.9             | Graphical representation and post-processing<br>of simulation results and measurement data53 |

|   |     |        |                     | Application Example55                                                                        |

|   |     | 5.3.2  | Application for EMC | tion of the EMC-Workbench<br>C-Adequate High-Speed Board Design58                            |

|   |     | 5.3.3  | EMC-A               | dequate System Design59                                                                      |

|   |     |        | 5.3.3.1             | Generalized Design Process                                                                   |

|   |     |        | 5.3.3.2             | Model of EMC Optimization60                                                                  |

|   |     |        | 5.3.3.3             | Tools & Simulation Environment61                                                             |

|   |     |        | 5.3.3.4             | Computer Aided Requirement Description61                                                     |

|   |     |        | 5.3.3.5             | Computer Support within the Specification Stage61                                            |

|   |     | 5.3.4  | Rule Ba             | sed Advisory System63                                                                        |

|   |     |        | 5.3.4.1             | EMC-Review Process as basis<br>of an EMC-Advisory-System63                                   |

|   |     |        | 5.3.4.2             | Realization of the Transformation Phase65                                                    |

|   |     |        | 5.3.4.3             | Rule And Freacs Input Generator (RAFIG)66                                                    |

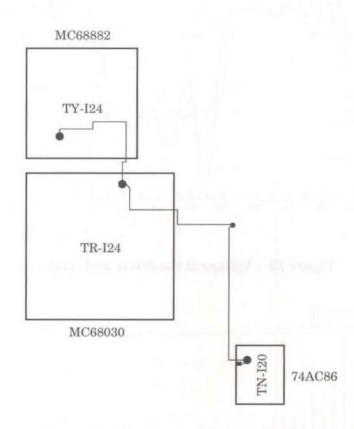

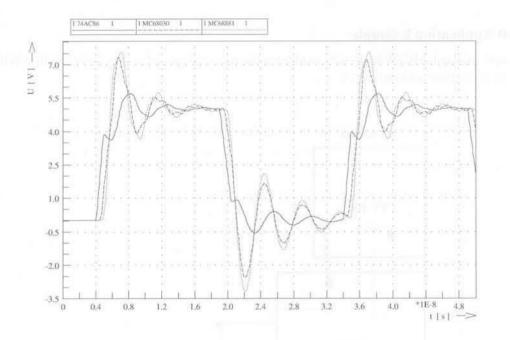

|   |     |        | 5.3.4.4             | Reflection Behaviour of Three-Point Nets                                                     |

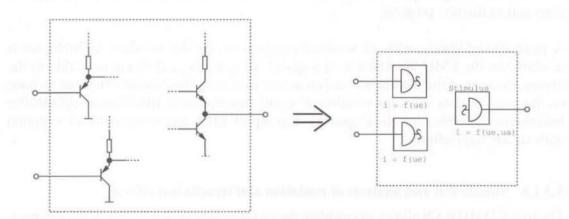

|   |     | 5.3.5  | Generati            | ion of Macromodels69                                                                         |

|   |     |        | 5.3.5.1             | Block-oriented Modelling Concept                                                             |

|   |     |        | 5.3.5.2             | Maromodelling Synthesis Environment MASE                                                     |

|   | 5.4 | Sumn   | nary and O          | Dutlook72                                                                                    |

| 6 | Tec | hnical | Managen             | nent Group and Computing Centre 75                                                           |

|   | 6.1 | Baseli | ine                 |                                                                                              |

|   | 6.2 | Work   | During th           | ne Report Period76                                                                           |

|   |     | 6.2.1  | CACE F              | Requirements Engineering76                                                                   |

|   |     | 6.2.2  | Software            | e Engineering and Quality Assurance77                                                        |

|   |     | 6.2.3  | Promotio            | on and Presentation                                                                          |

|   |     | 6.2.4  | Project A           | Acquisition and Coordination78                                                               |

|   |     | 6.2.5  | Computi             | ing Centre                                                                                   |

|   |     |        | 6.2.5.1             | Networking                                                                                   |

|   |     | 6.2.6  | Parallel            | Computing                                                                                    |

|   | 6.3 | Summ   | nary and C          | Dutlook                                                                                      |

| п |     | Iblications, Funded Projects and<br>Tientific Collaborations | 83  |

|---|-----|--------------------------------------------------------------|-----|

| 7 | Pub | olications and Major Documents                               | 83  |

|   | 7.1 | Cadlab Reports                                               | 83  |

|   | 7.2 | Major Software Documents                                     | 85  |

|   | 7.3 | Books, Conference and Journal Papers                         | 86  |

|   | 7.4 | PhD Theses                                                   | 92  |

|   | 7.5 | Master Theses                                                | 92  |

|   | 7.6 | External Talks, Lectures, Tutorials, Panels                  | 93  |

|   | 7.7 | Exhibitions                                                  | 94  |

| 8 | Fun | ded Projects                                                 | 97  |

|   | 8.1 | Nationally Funded Projects                                   | 97  |

|   | 8.2 | European Funded Projects                                     | 98  |

|   | 8.3 | Reports on Funded Projects                                   | 99  |

| 9 | Col | laboration in Technical-Scientific Bodies                    | 101 |

## Preface

When in 1985 Cadlab, the joint R&D institute of Paderborn University and Siemens Nixdorf Informationssysteme AG was founded this was driven by the intent to bridge the traditional gap between academia and industry by deeply integrating university research and industrial development. While university research is mainly driven by the desire to increase knowledge, industry has to be pushed by the market. It was the basic idea of the founders of Cadlab to combine these two cultures as closely as possible in order to maximize cross-fertilization and to stimulate innovation. Thus, in this unique joint R&D institute "Cadlab" engineers and scientists, although hired from both sides, work together day by day under one roof, jointly search for innovative solutions in mixed project groups and share problems and visions. During nine years of collaborative work Cadlab has proven that its founders' ideas not just remained a dream but became reality.

Cadlab's objective is to advance the field of engineering of computer based systems and to provide its partners with sophisticated solutions for solving complex engineering problems. During the report period numerous publications, including seven dissertations, have demonstrated the scientific success of Cadlab, while its achievements in precompetitive product development have been demonstrated by a couple of development cycles that reached a state mature enough to be ready for industrial exploitation. The EMC-Workbench may serve as one of the most impressive examples. This solution for a demanding and fast growing market has been transferred to a newly created spin-off company, called INCASES Engineering GmbH. Due to Cadlab's unique organisation and a consequent path from applied research to user oriented development, INCASES can offer today one of the most advanced solutions worldwide in this area.

From the beginning Cadlab's work has been inspired by the vision of providing smoothly integrated environments to the user in order to optimise the overall engineering process instead of isolated tools. Consequently, in the past research and development on tools always included the aspect of building integrated tool sets or "workbenches". Driven by requirements of its industrial partner Cadlab invested a large amount of its manpower in the design and implementation of the JESSI Common Framework which emerged into SNI's SIFRAME product. After technology transfer to its industrial partner in 1992 and appearance of framework technology on the market, Cadlab shifted its focus to additional advanced techniques of framework technology and on demanding application areas. As examples the following areas may serve: development of an open database middleware toolkit, the support of knowledge based engineering techniques, the realization of an operating system independent advanced editing toolkit, modelling of heterogeneous systems, the above mentioned EMC-Workbench and information exchange via standardised formats (STEP/EXPRESS).

At the end of the report period, about 70 scientists and engineers, and more than 100 student assistants and students preparing their master's thesis were employed in Cadlab. They are organised in two main groups, dealing with "Information Technology" and "Analog System Engineering". In addition there is a "Technical Management Group and Computing Center". 10 employees moved to INCASES during the last quarter of the report period.

Cadlab's results during the report period will be discussed in more detail in the following sections of this report. Therefore only some highlights shall be summarised here.

In future the coexistence and federation of established databases will be of great importance. This is due to the fact that the huge amount of data which is stored in existing databases forms an enormous investment, which on the one hand needs to be preserved, while on the other hand much more coordinated, efficient access facilities are urgently needed. Furthermore, database indepence and migration are strong requests needing an answer. Cadlab developed a technology to solve this set of problems by providing a modular toolkit called "Open Database Middleware Open DM". This approach was developed towards the pilot stage during the report period.

Knowledge based techniques also made considerable progress in the last years. By means of its IFS project Cadlab will offer an environment that supports the integration of knowledge based techniques into engineering systems. The architecture follows the proposals of the IEEE working group P1252.

As advanced user interfaces become more and more the key point of any computerised applications, Cadlab invested into the design and development of an advanced, platform independent graphical editing system. During the report period a major part of this system, the Editor Operating System EOS, was driven through two version cycles and successfully used to build first applications.

As complex computer based systems tend to be heterogeneous, a unified modelling approach seems to be necessary for creating a joint basis. On the other hand the unwieldiness of a large uniform model as well as the desire of the users to keep their preferred data views must be respected. Therefore Cadlab developed an approach that allows the various users to stay in the modelling environment they are familiar with, while internally a unified modelling paradigm is provided, whereupon all external model parts needing unification can be mapped.

The communication of data is increasingly based on STEP protocols. To support this trend a STEP/EXPRESS workbench has been designed at Cadlab. This software, too, has reached product quality and has been licensed worldwide to interested organisations.

Last, but not the least, Cadlab's most complex software system transferred to the market in this report period is the EMC Workbench. It is one of the leading design environments worldwide to support the design of printed circuit boards under EMC constraints. The successful use of this software within various departments of SNI and Siemens demonstrated its quality and fundamental importance. At the same time research towards a workbench supporting system design under EMC constraints has been continued. This research area covered e.g. parallel high performance simulation, an EMC advisory system, and a macro modelling environment. Cadlab's standardisation efforts have been concentrated on active participation in various international bodies. Areas of Cadlab's standardisation contributions included VHDL, STEP and EXPRESS, Data Modelling, Simulation Backplanes, Object Oriented Databases, Engineering of Computer-Based Systems.

Cadlab's international scientific reputation is reflected by the large number of publications. Cadlab employees have presented papers on most major international conferences on topics related to Cadlab's focus of research. In addition, Cadlab members have been active in organisational bodies of such conferences.

1994 was a year that demonstrated the intent and ability of Cadlab to anticipate upcomming demands and interests of Cadlab's constituting partners as well as trends and developments of the international research and user community. By concentration on leading edge pre-competitive areas the workforce could be focused on future-oriented goals. On the other hand, Cadlab has kept its proven main principles: tight integration of academic research and industrial development and focus on application oriented research and development topics.

The following annual report gives an overview of Cadlab's activities and achievements in 1994. Part I of the report details Cadlab's objectives, describes Cadlab's organisational structure and gives a general overview of the progress made. Part II contains technical details from the project groups. Part III provides supplementary information on publications, funded projects, and cooperations.

F.J. Rammig and B. Steinmüller Cadlab Executive Board Paderborn, May 1995 The particular interdistion of the first of the second second ball of the particular of the first of the second ball of the sec

Gentide-outomprimed scientific republicities and coal to an incorrenation of publications (into-tradict supply sets have to science pipes an excitation of an antiexcitation termoure to diabot force of responde to collation. Coald, and the force (good and of a minimation biother in such responde to collation.

12.2 Service can make demonstrate the relevant of the relevant of the control of the relation of the relati

Cardinal Second Second Second Second Internation of Cardinal Second Sec Second Seco

Bunnie and B. Someniter

Cullin Exemption Brinni

Referbore, May 1914

# I Overview

# 1 Goals and Objectives

## **1.1 Principal Goals**

Cadlab, the joint research and development institute of Paderborn University and Siemens Nixdorf Informationssysteme AG, SNI, has been founded in 1985 with the backing of the federal state of North-Rhine-Westphalia.

The vision behind this unique endeavour has ever since been to deeply integrate university research and industrial development within a joint centre of excellence for the synergetic benefit of the partners as well as the public.

The mission is to provide innovative computer-based solutions for challenging industrial problems and to support bi-directional technology and know-how transfer from academy to industry.

Cadlab's mission materializes in the following tangible R&D results:

- reports,

- · publications and PhD theses,

- software prototypes,

- · software components with industrial quality standard.

Moreover, it is Cadlab's objective to supply high-quality R&D services in the following areas

- consultancy,

- education and training,

- · coordination and support of complex R&D projects.

### 1.2 Objectives of the Report Period

The objectives of this report period were determined by the new strategic R&D directions and work programmes defined in the recent report periods as well as the actual requirements and needs by Cadlab's partners and customers. In particular, key objectives were

- to consolidate the work organization in the area of information engineering

- to provide software pre-products and pilot software in the areas of data base federation, advanced editing systems, and product modelling

- found a spin-off company for the commercialization of the key results achieved in the area of analog system engineering

- · initiate a new work organization and new work topics in ASE

In view of the upcomming termination of several projects executed within the third framework programme of the European Union, the preparation for the forth European framework programme as well as for new national programmes was a major task to be taken up.

# 2 Organization

### 2.1 Overview

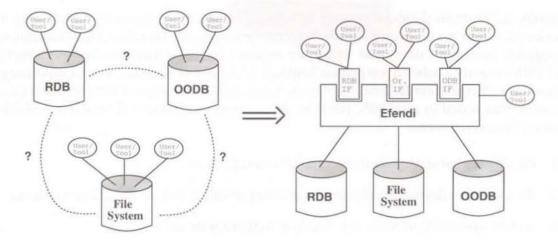

Cadlab is a joint venture of Paderborn University and Siemens Nixdorf Informationssysteme AG (SNI). Each partner provides scientific staff and corresponding financial resources to about equal parts. The cooperation is regulated by a contract closed between the two partners in agreement with the state of North-Rhine-Westphalia in 1985. It is open for new interested partners.

According to the guiding vision of deeply integrating university research and industrial development, a joint organization has been established, which enables Cadlab to act as one uniform organizational entity in a similar manner as an independent enterprise (see Figure 1). In formal external relations (e.g., in contracts with third parties), however, Cadlab does not act as a legal entity, but is formally represented by its two partners.

Figure 1 Cadlab, Principal Organisational Structure

Cadlab is headed by an executive board of two directors, one from the university and one from SNI. The executive board of directors is assisted and controlled by an advisory board, in which the interests of the partners are balanced.

All technical work is carried out in mixed project groups irrespective of the employment contract (industry or university) of the individuals. These mixed project groups are headed by project group leaders. Depending on the specific needs, these principal entities can be combined into larger "super project groups" or further sub-structured into smaller working groups. In particular, the project groups in the domains of "Information Technology" and "Electrical Engineering" have been combined into the corresponding super project groups "Information Technology, IT" and "Analog System Engineering, ASE" respectively.

### 2.2 Board Members

During the report period the following members were assigned to the Cadlab Executive and Advisory Board respectively.

Executive Board of Directors:

- Prof. Dr. F. J. Rammig, Universität-GH Paderborn

- Dr. B. Steinmüller, Siemens Nixdorf Informationssysteme AG

Chairman of the Advisory Board:

· Prof. Dr. W. Hauenschild, Universität-GH Paderborn

Members of Advisory Board:

- Mr. G. Held, Siemens Nixdorf Informationssysteme AG (until December 94)

- Prof. Dr. U. Kastens, Universität-GH Paderborn

- Dr. W. Kern, Siemens Nixdorf Informationssysteme AG

- Prof. Dr. G. Mrozynski, Universität-GH Paderborn

- Mr. U. Rethfeld, Siemens Nixdorf Informationssysteme AG (since December 94)

- Dr. A. Sauer, Siemens Nixdorf Informationssysteme AG (vice chair Advisory Board)

- Prof. Dr. G. Szwillus, Universität-GH Paderborn

Associated Members of Advisory Board:

- Prof. Dr. F. Belli, Universität-GH Paderborn

- Mrs. M. Brielmann, Cadlab (since January 94)

- Prof. Dr. J. Gausemeier, Universität-GH Paderborn (since December 94)

- Prof. Dr. G. Hartmann, Universität-GH Paderborn

- Prof. Dr. W. Hauenschild, Universität-GH Paderborn (chair of Advisory Board)

- Mr. H. Heckl, Siemens Nixdorf Informationssysteme AG

- Mr. T. Kathöfer, Siemens Nixdorf Informationssysteme AG (until December 94)

- Prof. Dr. H. Kleine Büning, Universität-GH Paderborn

- · Prof. Dr. T. Lengauer, GMD

- Prof. Dr. B. Monien, Universität-GH Paderborn

- Prof. Dr. F. J. Rammig, Universität-GH Paderborn

- Dr. B. Steinmüller, Siemens Nixdorf Informationssysteme AG

- Mr. H. Vogt, Siemens Nixdorf Informationssysteme AG

- Mr. J. Wening, Cadlab (until January 94)

### **3** Summary of Progress

Work in the report period was driven by the mission and goals summarized in chapter 1 above.

A key decision taken at the beginning of the report period was to form a new super project group called "Information Technology IT" (see Chapter 4) by merging two former closely related Cadlab main groups, and to subsequently form new subgroups in the areas of "Data Integration and -Modelling DIM", "Human-Computer Interaction HCI" and "Process- and System Modelling PSM". This way closely linked know-how areas could be united and strengthened, while at the same time the coarser organizational bundling created more degrees of flexibility for addressing new challenges on the project level.

Key results that were provided by IT included advanced software prototypes and first product components in line with the given work programme. Moreover, a large number of research results - including five dissertations - have been published.

In the area of "Data Integration and -Modelling DIM" (see Chapters 4.2) considerable progress was made in the construction of an advanced software environment for product data modelling based on the international ISO-standards "STEP" and "EXPRESS". Here the front-end of the Cadlab STEP/EXPRESS-Workbench was successfully completed and made available to beta-users on an international scale. In the future this workbench will be able to easily connect to a wide range of heterogeneous, distributed databases as found in any large company. The mechanisms for this connection are currently developed under the name "Open Database Middleware (OpenDM)". OpenDM addresses the requirements of database federation, integration, migration and data independence and thus provides answers to urgent database management problems in industry and commerce. In the report period a first version of OpenDM was successfully tested in a pilot project in the SNI factories for midrange systems.

In the area of "Process and System Modelling PSM" (see chapter 4.3) the project on "Intelligent Framework Services IFS" was continued. IFS provides integrated object oriented software services for the processing of hybrid knowledge and the efficient construction of knowledge-based integrated applications. It extends the international IEEE/ IMKA standard on frames with description means for rules and uncertainty parameters and provides a ready-to-use IFS-tool kit to the application programmer. In the report period the design work has been completed and first prototype applications have been developed. Thereby particular attention has been given to new application domains, such as traffic modelling and optimization, where interesting industrial projects have been conceived. Besides IFS, work on extended predicate transition nets (Pr/T-Net) was continued. Pr/T-Net concepts have been generalized and their application to support tool management was shown.

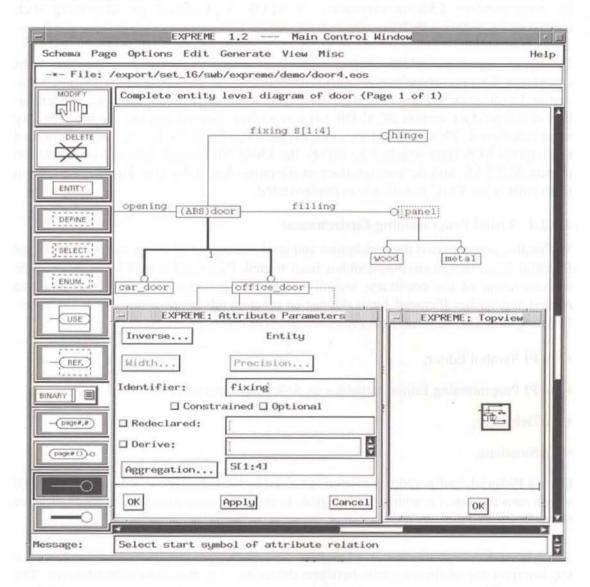

In the area of "Human Computer Interfaces HCI" (see Chapters 4.4), the project on "Advanced Editing Services AES" was carried on. A key achievement of this project was the provision of a comprehensive C++ library "Editor Operating System EOS" providing 350 classes and 4000 methods for the efficient construction of advanced platform independent editing systems. The EOS-libraries are already in use internally as well as externally. As an example, the graphical frontend EXPREME 1.0 of the STEP/ EXPRESS Workbench (see above) and the EMC-Editor SCALOR 1.0 (see below) were built with EOS.

New challenges for IT and Cadlab are given by the upcomming "information society", which will also revolutionize the way complex information contents is exchanged by using the emerging super information highways. In the report period, Cadlab took part in the analysis and conception of new global electronic market places for complex information exchange. Cadlab helped to shape the new "GEN"-initiative on "Global Engineering Networks", whose mission is to initiate and coordinate new projects for the promotion of GEN-technology and GEN-marketplaces".

The activities in the domain of "Analog System Engineering ASE" (see chapter 5) are focused on the development of tools and methods for the design of electronic circuits and systems under EMC-constraints. EMC stands for "Electromagnetic Compatibility" and addresses a problem area, which has become ever more critical with the adventure of high speed electronic systems. Effective solutions in this area necessitate the anticipation of EMC-effects early in the design process by means of sophisticated computer aided design and analysis techniques ("concurrent engineering"). Moreover, there is a strong need for EMC-consultancy throughout the field.

The central result achieved within ASE in the report period was the successful finalization of the EMC-Workbench V1.2 and its transfer into a newly founded spin-off company. Moreover, three dissertations and numerous publications shaped the scientific reputation of the group.

While much energy had been invested during the last report periods to industrialize the results and to investigate effective pathes for the commercialization of this advanced technology, in this report period the decisive break-through was achieved. After intensive negotiations with investors, the company INCASES Engineering GmbH was founded in Paderborn in November 1995. Key development and consultancy staff was transferred to INCASES together with EMC-technology, in particular the EMC-Worbench 1.2. At the same time work on forthcoming versions, which will pay particular attention to systems aspects, continued. A close cooperation has been set-up with INCASES in order to safeguard the smooth technology transfer of new solutions.

Consultancy of SNI and Siemens factories also played a significant role during the report period. For example, the most critical parts of new SNI UNIX computers (RM Family) were successfully prepared and analysed for electromagnetic compatibility and signal integrity. The consultancy services have also been successfully transferred to INCASES at the end of the report period.

Besides the technology transfer task, the re-orientation of the ASE-group towards future topics was continued. Here, the development and application of EMC-technology to full systems on the micro- as well as the macro-level is of primary interest. In the report period most of the work focused on the micro-level. Moreover, a new organizational setup has been prepared.

Efficient support for the ongoing R&D work was provided by the Cadlab "Technical Management Group" and the "Computing Centre, CC" (cf. chapter 6). CACE-consultance provided to the SNI System Unit Midrange during this and the last report periods not only supported the application-oriented approach of our technical main groups, but also laid the basis for new joint consultancy projects, which will become effective in the next report period (project data management, application of data base middleware know how, a. o.). Moreover, internal quality assurance and computing support was provided.

During the report period most of the technical tasks and staff migrated into the technical groups. As a result a lean "project support group" has been founded, which is responsible for administrative and marketing support tasks.

While some of the central tasks have been transferred into the main groups by the end of the report period, "parallel computing" was taken up as a new technical topic for the CC-group. Initial studies have been undertaken in preparation of new project fields.

Most of Cadlab's work again was carried out in the context of collaborative projects (see chapter 8). Concerning nationally funded collaborations, Cadlab has participated in 7 BMBF projects, two of them executed in the frame of the European JESSI programme. Thereby, the large European EMC project JESSI AC-5 is also led by Cadlab. Three projects are funded by ESPRIT.

Publications and dissemination of technical/scientific results again played a major role also in this report period (see chapter 7). Cadlab's work is documented in about 120 public reports and papers. Cadlab software was demonstrated on more than 10 fairs all over the world including in Japan, USA, Canada and many EU-countries. More than 80 formal presentations, talks and tutorials were given on a large number of international events. At the same time internal technology transfer, education and training of young talent in application oriented engineering was actively promoted. This is reflected by 10 master theses written under the supervision of Cadlab members and 120 student assistants integrated in a large number of Cadlab software projects.

7

Water several hereauth and several and the second second second second several second second second second seco Delicity in the second secon structs for the second secon

Marke of Contract, with apple the control on a line matrix of them were provided by a start of the control o

Another and a more than an extension of the firm of a set of the s

# II Project Group Reports

## 4 Information Technology - IT

### 4.1 Introduction

The project group "Information Technology, IT" was formed in April 1994 as a merger of the two former project groups "Base Technology, BT" and "System Engineering Technology, SET". The rationale behind this merger was the fact that in both groups large potential for synergy and cooperation has been identified, which made it necessary and sensible to join forces.

In continuation of the existing activities started in BT and SET in 1993 three project groups have been founded with the following objectives:

- the Data Integration and Modelling group, DIM, combining the work of the former BT group Data Integration (DI) on data base federation services, DBF, with the STEP/EXPRESS data modelling efforts of SET; starting point of the work of DIM has been the joint objective of offering open data base middleware services for the efficient, transparent storage of, access to and interchange of data in heterogeneous data base environments; the heterogeneity relates both to data base technologies in use (file system based, hierarchical, relational and object-oriented ones) and the platforms (PC and UNIX systems) on which these data bases are operated.

- the group Process and System Modelling, PSM, which emerged from the two groups Control Integration (BT CI) and System Engineering Technology (SET); both groups were dealing with two different views on heterogeneous IT systems: An operational view modelled by Extended, Timed Predicate/Transition-Nets (Pr/T-Nets) and a declarative view expressed by rules and frames; in combining these approaches, PSM performs research and development in the area of computer-based system specification, evaluation, generation, and control; the target is the development of integrated, generic environments for system development and system control;

- and the Human-Computer Interaction group, HCI, as natural successor of the BT group User Interface (UI) to give credit for its broader topics like gesture-based editing and visual programming, both in development and research; in parallel, all Cadlab efforts on editors and graphical representation means as generally available services for all the other Cadlab project groups have been bundled in this group;

All the efforts spent and work done by IT during the report period were originating from BT's former mission to investigate infrastructures needed for the engineering of computer-based systems and to provide basic services for building engineering environments and from SET's mission to perform research and development in the field of concurrent system engineering methods and tools.

## 4.2 Data Integration and Modelling - DIM

### 4.2.1 Baseline

The access to and modelling of data gains increasing importance since database applications are not even more restricted to single data sources. An increasing number of database applications is confronted with problems in the area of

- data access to and manipulation of multiple heterogeneous databases

- integration and modelling of data crossing multiple data bases

- exchange of data between application domains and user sites

- migration of data and migration of applications

In most of these cases either multiple database applications or multiple databases are involved. A scenario were multiple applications run on multiple databases makes this expressive. We use this scenario as a guidance for our R&D work. The idea is to provide a software layer as a kind of database middleware between applications and data handling systems (database systems, file systems, etc.) which allows to reduce the efforts and costs for designing and implementing database applications.

#### 4.2.2 Work during the Report Period

#### 4.2.2.1 Database Federation Services

The "Database Federation Services (DBF)" project started in January 1993. The aim of the project is the federation of heterogeneous, autonomous database systems (DBS).

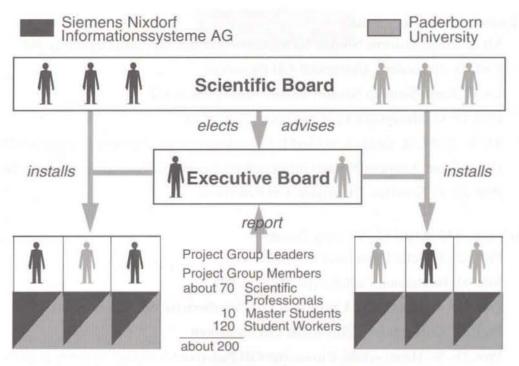

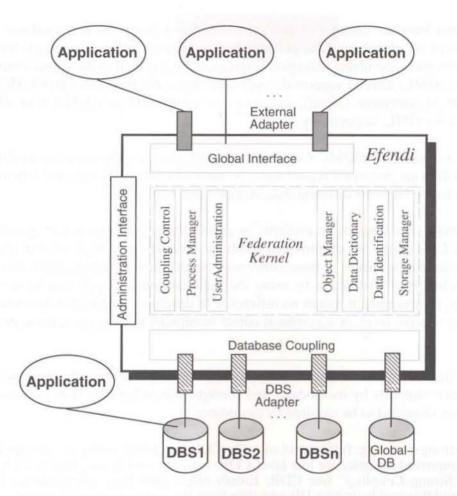

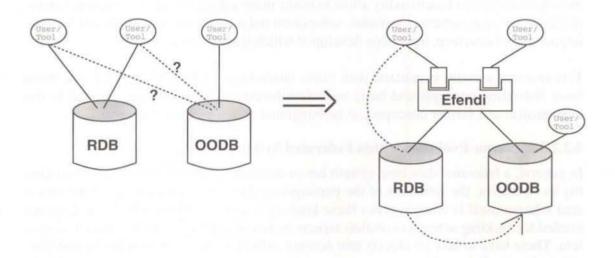

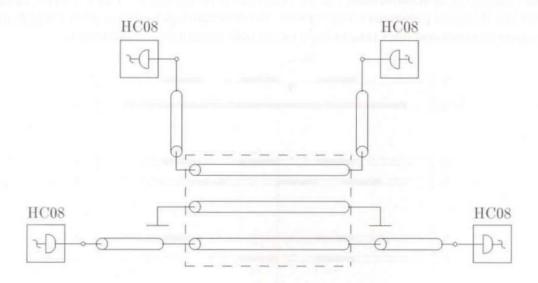

Object-oriented database systems together with database systems based on the most relevant relational or the entity-relationship model are candidates for the federation within the DBF project. Efendi - one result of the DBF project - offers a solution in form of a flexible software layer on top of these heterogeneous database systems. It allows to preserve the autonomy of these "component databases (CDB)" so that their existing applications can continue to run locally (keyword: preservation of investment). On the other hand, it offers uniform and transparent access to the "federated data" of the CDB for new (global) applications. The architecture of Efendi can be seen in Figure 2.

**Figure 2: Architecture of Efendi**

The model contains the following modules:

- · Administration Interface: supports administration facilities

- global interface: providing multiple federated and external schemata and furthermore operations according to them;

- external adapters: data model conversion between standard database interface, e.g., STEP/SDAI used by a global user and Efendi Global Interface; an External Adapter is only needed if the Global Interface and the user required database interface differ;

- federation kernel: connecting link between user resp. application and CDB, deals with necessary mappings and transformations;

- database coupling adapters: data transport and conversion between heterogeneous, federated data base systems and Efendi (with a canonical data model);

- CPU DB: storing global data, meta data and schema information of Efendi.

The global interface consists of two parts: one for defining the federated and external schemata of the global interface and one for object manipulation according to these schemata. Both parts, the object definition language (ODL) as well as the object manipulation language (OML) directly support the industrial object database standard ODMG (Object Database Management Group), i.e., they are compatible to ODMG C++ ODL and ODMG C++ OML, respectively.

Instead of coding the ODMG C++ OML by hand, interfaces for schema consistent data manipulation are generated according to the defined schema. By this, one schema definition can be the basis for different data manipulation interfaces.

Furthermore, functionality is available to extend the global interface by graphical features. A C++ library which provides graphical concepts on a high level of abstraction was developed. By means of these concepts it is possible to develop graphical editors on different levels of abstraction by using the same concepts. Concerning these graphical concepts, for example, it makes no difference to develop a graphical schema editor representing schema level, or a graphical object manipulation language representing object level.

The application of Efendi is not restricted to the federation of some database systems but Efendi also supports by its modular and configurable nature two other solutions which have been identified to be required by customers:

strong-coupling: full control over the CDB by Efendi, no local users/applications, improved integrity for low level CDB, e.g., file system (see Figure 2); by way of "Strong-Coupling" one CDB, Efendi offers data base independence (database middleware) by hiding DB-specifics form the application programmer;

• migration: tool and data migration (see Figure 3).

no local users

no autonomy of CDB (more concurrency control)

#### **Figure 4: Tool and Data Migration**

The DBF project follows the SNI Process Technology and is now in the "Implementation Phase". In parallel to this phase, the development of a graphical Efendi demonstrator and a pilot project with a SNI department has been started. The demonstrator couples the relational database ADABAS-D and the object-oriented database SIFRAME-OMS.

In the pilot project also a relational database DDB/4 has been coupled with a file system based electronic library and a relational PC database ACCESS.

#### 4.2.2.2 Federation of and Migration Within Multiple Database Systems

While existing approaches treat the federation and migration among multiple heteroge-

neous, autonomous database systems as separate issues, these, currently more research oriented efforts are to investigate how both can be combined. Therefore, basic federation concepts have been developed which are required for any federated database system (FDBS), mainly a schema integration language and a global interface. For incorporating novel object migration facilities into them, it was at first investigated what and how data can be transferred in an FDBS. Baseline was a migration framework which is scalable along three dimensions:

1. the object kind stating what object data is stored where,

2. the migration degree specifying how much of an object to transfer and from where,

3. and the operation primitive defining how to transfer the data.

At Cadlab, implicit and explicit migration operations which enable users/administrators to transfer data among the various database systems in various granularities have been developed during the report period. All migration operations preserve the objects global identity. Thereby data locality change is hidden from global FDBS applications so that they do not have to be recoded. While the basic federation concepts in combination with the object migration functionality allow to cover many migration cases, extended federation concepts, e.g., schema extension, subsequent redundancy identification, and a multi-lingual global interface, have been developed which make it even broader.

This research activity is realized with many interactions to the DBF project. The main basic federation concepts and basic migration functionality are already adopted in the DBF project and further concepts can be integrated seamlessly into future versions.

#### 4.2.2.3 Schema-Evolution within Federated Systems

In general, a federated data base system has to deal with a number of modifications during its operation: the schemata of the participating data bases may change or the federated schema itself is changing. For these kinds of schema evolutions basic methods are needed for tackling schema evolution aspects within the overall federated data base system. These have to take all objects into account, which are affected by schema modifications. In parallel to the necessary research in this area prototype-like software components are being developed for sample practical judging of the chosen approaches in order to get early feedback.

#### 4.2.2.4 STEP/EXPRESS Environment

The project STEP/EXPRESS Environment was started in the beginning of 1993.

The emerging international standard for the exchange of product model data is ISO 10303 "Industrial automation systems and integration -- Product data representation and exchange", better known as STEP (STandard for Exchange of Product data). STEP provides standardized data schemas, called *Application Protocols (APs)*, for a number of application domains. For defining the data schemas, STEP provides the information modelling language EXPRESS. Thus, the APs are annotated EXPRESS schemas.

The STEP implementation methods define the implementation of data exchange and data access. The implementation methods are independent from any specific EXPRESS model. Part 21 of STEP defines how an ASCII file format is derived from an EXPRESS schema.

Thus, an AP together with Part 21 defines a standardized file format for data exchange. Part 22 of STEP defines the database interface SDAI (Standard Data Access Interface), which provides a standardized access to data that conform to an AP.

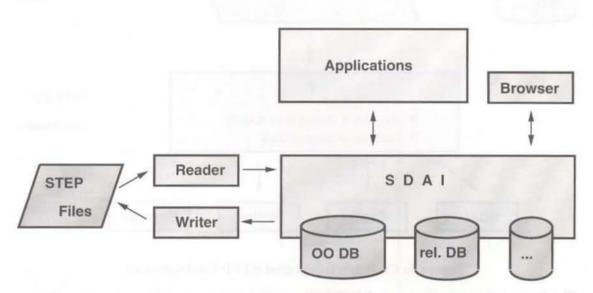

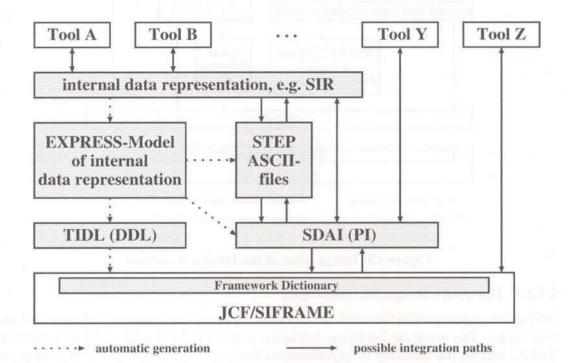

Figure 5 shows the Cadlab view of a STEP implementation. The data are stored in a database or a number of (heterogeneous) databases. The application(s) access the data via the Standard Data Access Interface SDAI. For the data exchange, a writer and reader are provided that write the data to be exchanged in a STEP File or read it from a STEP File.

Figure 5: Product Data Access and Exchange

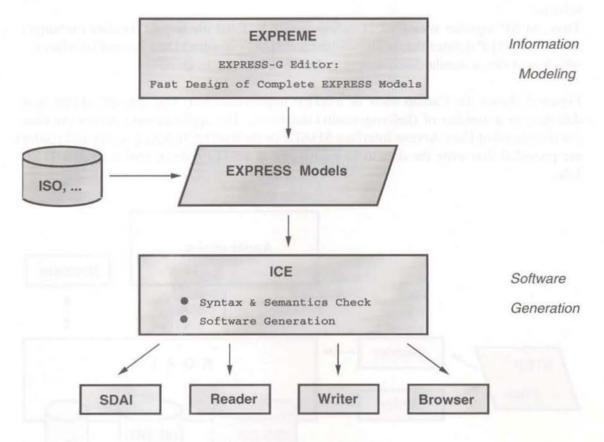

The basic idea of this work is the generator approach. Since an EXPRESS model automatically defines the file format for data exchange and the SDAI, the corresponding STEP software can be generated automatically from EXPRESS models. Therefore, Cadlab does not implement the SDAI or reader/writer themselves, but implements generators that generate this software from the application data schema (EXPRESS model). Figure 6 gives an overview of the integrated Cadlab STEP environment.

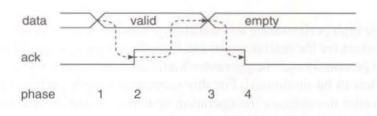

For the design of EXPRESS models, the EXPRESS-G editor EXPREME was developed in cooperation with the HCI group, see Chapter 4.3.2.2. In 1994, the delivery of EXPREME 1.0 was started. Now EXPREME 1.2 is marketed by SNI. Over 70 licenses are installed world-wide.

In 1993, the EXPRESS syntax and semantics checker ICE was developed. Since November '93, ICE is available free of charge for Sun-4, SGI, HP9000, Apollo, IBM RS6000, OS/2, and Linux. The ICE software can be retrieved from the ftp server of Paderborn

University via anonymous ftp. During the report period, ICE was adapted to the ISO 10303-11 International Standard, and ICE was prepared to serve as front-end for the generators.

Figure 6: Cadlab's Integrated STEP Environment

The first generator built was an EXPRESS-to-TIDL generator. TIDL is the Data Definition Language of SIFRAME/OMS. The EXPRESS-to-TIDL generator was completed during the report period and was delivered to a number of users within SNI.

Furthermore the development of the SDAI generator was started during the report period. SDAI is the Standard Data Access Interface of STEP. A generator is being developed that generates a C++ early-binding SDAI implementation from a set of EXPRESS schemas. This generator is based on the software realised within the DBF project: A generator was developed that generates the ODMG C++ OML from an ODL data schema, the SDAI generator generates the SDAI from an EXPRESS data schema in a similar way.

#### 4.2.2.5 Transaction Management in Design Environments

An important aspect of design environments is design transaction management. Design transactions are different from traditional transactions as they have to support long-lived and cooperative activities. Known algorithms for concurrency control and recovery are too restrictive for such environments. Thus, a lot of advanced transaction models have been developed throughout the last few years that try to support design and other cooper-

ative applications. However, a satisfactory model offering the flexibility needed by design environments is still an open research issue. In particular, there are only few approaches to the problem of recovery of design transactions.

Cadlab has therefore developed a transaction model for the area of design which is based on the transaction toolkit approach (developed at the University of Hagen). The model offers flexible concurrency control and recovery strategies which can be configured in an application-specific way. The model also aims at the integration with an object-oriented database system (following the ODMG Standard) in order to exploit semantic information from the database schema. In order to demonstrate the practical applicability of the concept, Cadlab has developed a prototype of the transaction model.

#### 4.2.2.6 An Open Object-Oriented Integration Environment

Integration of tools into a design environment means to add tools into this environment and let them interact with other tools within the environment. This includes the organisation of data so that they can be shared by different tools as well as a common control mechanism for the coordination of control flow of tools. Whereas the organisation of data mostly is a structural aspect, the coordination of tools mainly is a behavioural aspect. Both aspects must be combined into a common abstract data model. The objectoriented approach supports both aspects in a proper way but it lacks a standardised object-oriented data model so far.

These requirements motivated the investigation of an integration model containing object-oriented basic concepts which can be applied recursively to be configured to domain specific data models and data schemas. These concepts are on one hand still object-based and allow on the other hand the definition of particular concepts. As a result of the recursive approach the structural and behavioural coordination of different data models and data schemas as well as the definition of different application domains is handled in a unique manner. Based on these basic concepts different levels of tool integration, the integration of domain specific and domain neutral tools, as well as the specification of tool-specific interfaces to data shared by several tools are supported.

### 4.2.2.7 A Rule Meta Model for Active Database Systems

Rules are used in active database systems to monitor situations of interest and to trigger a timely response when these situations occur. They can be applied for several problems, e.g., consistency checks, derived data, change notification or recovery. The integration of rules into database systems does not only have advantages - the main drawback is the introduced complexity which makes it more difficult to understand what happens in the system and which is the source of additional inconsistencies as, e.g., infinite loops, where rules trigger one another indefinitely. A rule model defines the semantics of the rules and how a collection of rules is treated at run-time. Rule meta models offer a set of parameters which can be used to define rule models.

Rule meta models are useful for a couple of reasons, e.g., they offer a good baseline to compare existing rule models, they can be used as baseline for the analysis whether rules may trigger one another infinitely and they can be used to define rule semantics which

best fit to the requirements of the applications. Existing rule meta models only offer parameters for parts of the semantics of rule models, and some of these parameters do not describe elementary rule model aspects. Therefore, a rule meta model has been developed which should fill this gap. This model uses Petri Nets as a formal method for a precise specification of many of the different aspects of rule modes.

#### 4.2.2.8 Semantics and Definition of Structural Defined Views

The majority of view models for object-oriented database systems (ooDBS) has extended the semantics of relational views by utilizing and applying the new opportunities of ooDBS, e.g., object identity. New features of view models also support the use of views for advanced applications that go far beyond the traditional relational views. In particular, views are conceived as application specific schemas on top of the conceptual database schema. But so far, no widely accepted notion of views in ooDBS exists.

In spite of the non-uniform semantics of views in ooDBS - a lot of new indispensable new features, new requirements, and new technical solutions - the majority of view models are based on the traditional mechanism for view definition: Views are defined by means of a query, i.e., the result of a query is conceived to be the view. But an object-oriented data model provides two mechanisms for view definition: an operational one, based on a query language, and a structural one, based on inheritance mechanisms. So far, the latter one hasn't received much attention in literature.

Current research activities at Cadlab concerning views in ooDBS focus on the structural definition of views. The following aspects are examined:

- What do operational and structural view definitions have in common and where do they differ?

- What are strength and weakness of operational and structural view definitions?

The research results show that operational view definitions lead to problems concerning pretentious data representation within the view while structural view definition in its pure kind isn't suitable to define views that satisfy predicates on object values. To overcome the weaknesses of the structural as well as the operational view definition it is recommended to integrate both kinds of view definition in one common framework resp. architecture. The research activities lead to a view model for structural view definition that satisfies pretentious data representations, e.g. restructuring of objects and attributes. According to the proposed architecture, the view model can be integrated with operational mechanisms for view definition.

### 4.3 Process and System Modelling - PSM

#### 4.3.1 Baseline

Since information technology plays a key role in linking several technologies like mechanics, communication, transport, or business systems, engineering environments have to consider these heterogeneous application domains. In order to tackle this variety of technical and organizational systems an integrated core environment is being developed. This core environment provides application independent models, methods and tools that can be easily specialized for the envisaged application domains, e.g. in order to provide a user with the specification formalisms he or she is used to. The core environment will be applied in the development of mechatronic, hardware engineering and transportation systems. The methods and tools of the core environment are not only useful for heterogeneous system development but also proved their applicability for the control and guidance of system development processes.

Depending on the point of view towards the systems under design, different requirements arise with regard to the specification and interpretation of system models. If primarily the system behaviour is regarded an operational model is preferable. If the concrete system behaviour (e.g., sequencing, parallelization or timing of actions) should be abstracted a declarative view seems to be more appropriate. Accordingly the core environment provides two formalisms for system specification, evaluation and generation. Extended timed Predicate/Transition-Nets (Pr/T-Nets) are used to describe behavioural aspects of systems or system parts. Rules and frames are provided as declarative modelling formalism. One major advantage of these modelling formalisms is that the semantics of system descriptions is clear and unambiguous since also the interpretation of these models is formally defined.

However, these modelling formalisms do not allow to tackle raw information like pictures, which will become more important with the extended use of multimedia environments. Therefore, the core environment will be extended by mechanisms to analyse pictures of systems or system parts and to combine this information with the corresponding symbolic description.

#### 4.3.2 Work during the Report Period

During the report period work was carried out on software platforms for the declarative and the operational branch of the core environment, that are described in respective paragraphs on "Intelligent Framework Services" (see chapter 4.3.2.1) and "Pr/T-Net Modelling and Simulation Environment" (see chapter 4.3.2.2). Some applications of the underlying modelling paradigms for system specification and evaluation will be described in the paragraph on "System Modelling and Evaluation" (see chapter 4.3.2.3). Design activities concentrated on the observation, development and realization of "Hardware Design Methodologies" (see chapter 4.3.2.4). As a cross-cut activity through different application domains and engineering activities work was performed on "System Design under Timing Constraints" (see chapter 4.3.2.5). Further work was performed on the "Evaluation of the JESSI-Common-Framework".

#### 4.3.2.1 Intelligent Framework Services (IFS)

The "Intelligent Framework Services (IFS)" project started in January 1993. The aim of the project is to provide hybrid knowledge representation and evaluation services and to help system developers in building knowledge based tools. For the IFS project no new knowledge processing approach has been looked for, but instead the system is built on top of the concepts which have already proven as an expressive means of dealing with knowledge, namely on *frames* and *rules*. However, different to all other known hybrid knowledge-representation system known, the frames and rules components of IFS are deeply integrated using the object-oriented paradigm, and their integration incorporates possible extensions to handle uncertain knowledge. To ensure that end user needs are considered, a set of application examples have been built using IFS.

The work for IFS was largely carried-out in the JESSI Common Frame (JCF) project. Within the subproject 'Applied Research' (SP1) prototype software was provided which consists of a knowledge representation and access component (KAL) and a knowledge evaluation component (KEC). Within the subproject 'Development' (SP2) a transfer plan for IFS software components was defined which follows the SNI Process Handbook, PHB. According to these guidelines the prototype software developed within SP1 was improved and additional documentation required by the PHB was provided.

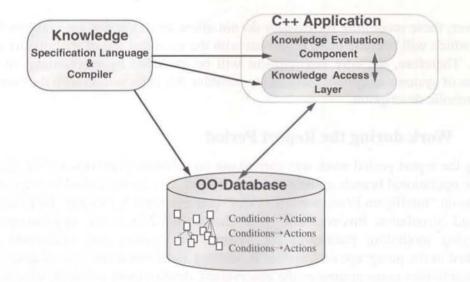

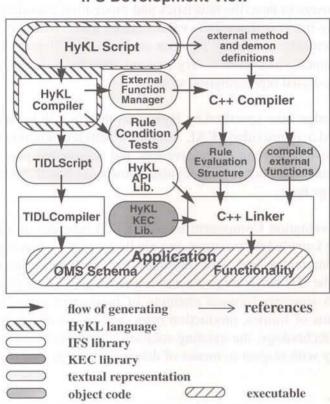

The problem independence of the IFS basic services allows for the development of various kinds of knowledge based systems differing in knowledge structure, problem solving strategy, and last but not at least the target domain. Nevertheless, all conceivable applications share the same basic components and properties. Figure 7 gives an overview of the main IFS software components, figures 8 and 9 give further details on the development and runtime views respectively

Figure 7: The IFS Software Components

To specify the knowledge base of an application and the desired inference control, a specification formalism is needed. In the IFS system, the knowledge specification lan-

guage, HyKL (Hybrid Knowledge Description Language), is used to this end. A HyKL specification forms the knowledge schema of an application. A HyKL compiler translates this description into a persistent knowledge base residing in an object-oriented database. The IFS system is currently based on the JCF Development System, mainly on its object management system, OMS and on the object definition language TIDL. Therefore, the HyKL compiler is a cross compiler which generates TIDL code.

For the development of the frame-part of HyKL, a proposed IEEE standard is used as a base. This standard for a frame-based knowledge representation is developed by the IEEE working group P1252. Frames are the fundamental representational structure of choice for a wide variety of representational tasks. Each frame represents a concept and consists of a collection of attributes and their values, that are associated with that concept. Rules allow users to describe heuristics and procedural knowledge of a domain. If rules and frames are integrated, attribute values can be tested within rules. Rule premises inherently define semantic proximity between attributes of different objects. Thus, when integrated with frames, rules give a very general way for defining arbitrary semantic relations in a frame-based representation system.

To access a knowledge base specified by HyKL, an interface in form of the Knowledge Access Layer (KAL) is provided. KAL combines different knowledge representation paradigms to achieve both high expressiveness and reasonable performance, enabling the development and integration of employable knowledge based systems consisting of a persistent knowledge base.

The Knowledge Evaluation Component of IFS (KEC) provides an inference engine to efficiently evaluate knowledge structures, but applications may also implement their own problem solving strategies and user interface for knowledge acquisition and case description using the IFS Knowledge Access Layer (KAL). The Knowledge Evaluation Component of IFS supports forward chaining of production rules. Since HyKL integrates the paradigms of frames, production rules, and uncertain knowledge with object oriented database technology, the existing solution algorithms for forward chaining are extended especially with respect to means of database integrity and concurrency in multi user scenarios.

Some of the components mentioned are represented in Figure 8. Additionally, Figure 8 shows how an application is generated:

An IFS application developer writes a HyKL script from the conceptual model of the system to be built. He or she models the domain structure with HyKL frame structures and heuristics of the domain with HyKL rules. Procedural behavior of frames may be specified in method slots by triggering sets of rules or by writing functions or member functions in C++. For many problems and algorithms, the latter is more convenient than rules.

The knowledge base is completely accessible from C++ by function calls to the HyKL API. Method slots and slot demons defined by a C++ function must be adequately declared in the HyKL script. In Figure 8, this is illustrated by a thin arrow labelled 'refer-

ences' in the legend. As further shown in Figure 8, the HyKL compiler generates a TIDL script. This TIDL script will be provided with all necessary information to identify a function according to a particular method or demon at runtime. Additionally, it contains the database representation of HyKL rules. Further, the HyKL compiler generates a so called external function manager, which dispatches all calls to methods and demon triggers to execute the appropriate function with the correct parameters during runtime. For HyKL Rules, the compiler also generates an internal, C++ coded structure for efficient matching of rule conditions. This structure and the external function manager have to be compiled and linked together with the function definitions coded in C or C++, the HyKL API library, and the library providing the runtime functionality of the Knowledge Evaluation Component KEC.

#### **IFS Development View**

Figure 8: The IFS Development View

The rough module structure of the resulting IFS application is shown in Figure 9. The software consists of the pure application part, designed by the application developer. It has to be noted, that it may contain arbitrary C++ programming and OMS accesses besides frame and rule accesses, if needed. Access to the entire frame structure including schema information, instances and relations as well as to sets of rules, single rules and parts of rules is ensured by the HyKL API. The HyKL KEC provides for efficient rule evaluation by forward chaining. The KEC and the API should be divided in a database independent and a database dependent part, for reasons of portability. The External Function Manager which dispatches demon calls triggered by database accesses or method calls is generated by the HyKL compiler.

The approach pursued by the IFS project has been justified by applying the developed IFS technology in two areas: An advisory system for EMC evaluation purposes and traffic optimization employing intelligent services have been successfully demonstrated.

|                                                  | IFS Runtin                               | ne View                                          | and a shearby                   |

|--------------------------------------------------|------------------------------------------|--------------------------------------------------|---------------------------------|

| Application                                      | on                                       | Frames &<br>Rules                                | External<br>Functions           |

| database<br>independent<br>database<br>dependent | HyKL API<br>Knowledge<br>Access<br>Layer | HyKL KEC<br>Knowledge<br>Evaluation<br>Component | External<br>Function<br>Manager |

| Database                                         | (OMS)                                    | -                                                |                                 |

Figure 9: Functional Architecture of an IFS Application

#### 4.3.2.2 Pr/T-Net Modelling and Simulation Environment

During the report period a prototype of a design environment for extended Pr/T-Nets was developed. With this environment it is possible to specify and simulate extended Pr/T-Nets. The main features of extended Pr/T-Nets are:

- set operations at transitions,

- · hierarchical places and transitions,

- · time dependent firing of transitions,

- recursive definition of hierarchical nets.

The Pr/T-Net environment is based on a common data schema that covers the management of design data in general and a data schema for the net representation itself. These schemata will be described first before an overview of the Pr/T-Net environment is given.

#### Schema Development:

Complex systems consist of a lot of different components from different application areas which might be handled by different tools of the system engineering environment. These tools might work on a common data format. But very often they also need their own description format. This makes clear that a lot of data and files have to be handled during the system development process and that a management schema is urgently needed.

Within the report period a schema for the management of the data has been developed based on a structurally object oriented database. This schema allows the identification of the components and the system they belong to. The schema supports the hierarchical development of systems by offering an instantiation hierarchy. Systems or system parts may be designed in a top down manner or they may be constructed in a bottom up approach. The interface and the implementation of a component can be stored separately and different alternative descriptions of system components can be handled. This enables the definition and comparison of multiple implementations for a given interface. Already existing system components or those that reached a stable design status can be archived in libraries.

As a common model for system specification from the behavioural/operational point of view extended Pr/T-Nets are used. To allow different tools to work simultaneously on these specifications a schema based on the object oriented database has been developed. This schema covers the Pr/T-Net structure as well as its dynamics. The structural part contains objects for the elements of Pr/T-Nets which are places, transitions, edges and the ports of the interface. Special instantiation relations are introduced to allow access to the instantiation facilities of the data management schema and thus to the instantiated subnets. The schema part for handling net dynamics allows to manage graphs of net states. Each net state consists of objects representing the actual marking and the transition status.

For both schemata, the management schema and the net schema, C++ classes for the schema objects and access methods as programming interfaces have been developed and implemented. Based on these programming interfaces the Pr/T-Net Environment described in the next paragraph was realized.

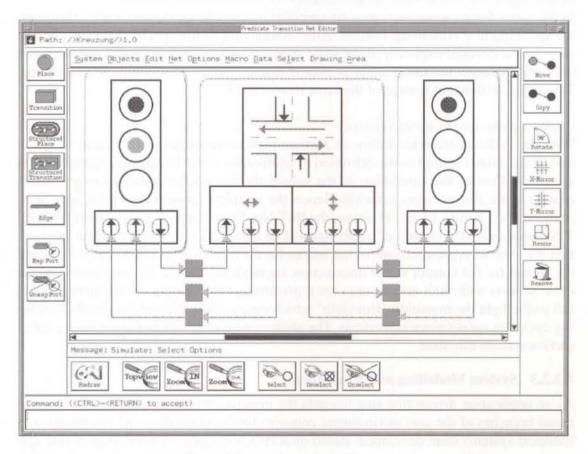

#### **Overview of the Pr/T-Net Environment:**

The current environment consists of a browser for the selection of existing or new nets or subnets, a Pr/T-Net-Editor for a comfortable editing and simulation of Pr/T-Nets, and a Pr/T-Net-Interface-Editor for the definition of abstract graphical representations for subnets. Some important features of the design environment are:

#### Mixed Editing and Simulation of Extended Pr/T-Nets:

With the Pr/T-Net-Editor it is possible to edit and simulate the net alternately without intermediate compilation steps. During such an edit-simulate-sequence it is even possi-

ble to change the actual net marking and continue simulation on this new marking. Markings reached during the simulation can be saved and reused as starting points for further simulation steps together with new markings generated with the editor. This feature allows a very flexible handling of stimuli which is especially valuable during the development phase of a system.

#### Mixed Top-down and Bottom-up Specification of Hierarchical Pr/T-Nets:

In the same design some parts may be specified in a top-down manner while other parts are specified in a bottom-up fashion. After completion of the specification the consistency can be checked explicitly. If the same subnet is used several times in a specification, only the dynamic net information is copied and the static information is instantiated. This avoids redundant storage of the same information.

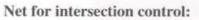

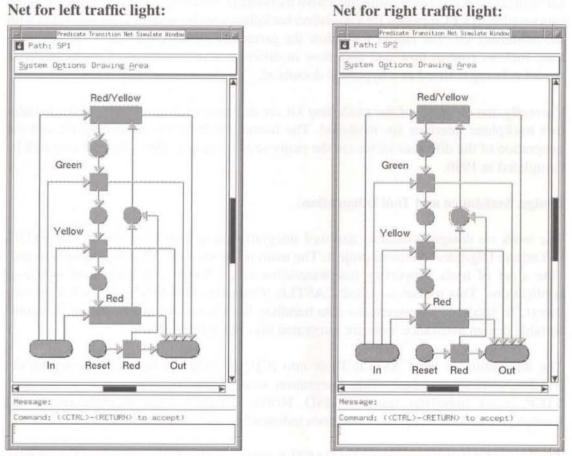

#### Abstract Representations of Subnets:

With the Pr/T-Net-Interface-Editor an abstract representation for a subnet can be specified. If the subnet is used in the definition of another net, only this abstract representation is visible. During the simulation of the subnet the firing of a transition may cause a change of the abstract representation. Hence, the abstract representation reflects the state of the subnet. Figure 10 and 11 shows the Pr/T-Net-Editor during the simulation of a Pr/ T-Net specifying the control of traffic lights at an intersection. In the net for the intersection the abstract representations of the subnet for the traffic light (instantiated twice) and the subnet for the control of the intersection are depicted. Below, the net definitions for these subnets with their actual states are represented. For example, in the subnet for the left traffic light the transition "Rot/Gelb" which means "Red/Yellow" has finished its firing cycle (its output place is marked). The abstract representation in the net for the intersection reflects this state.

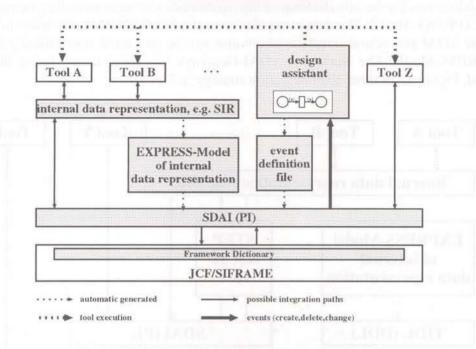

#### 4.3.2.3 System Modelling and Evaluation

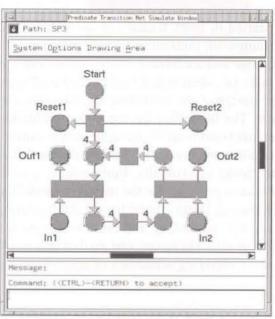

As an application driven first step towards the integration of the declarative and operational branches of the core environment concepts for the evaluation and optimization of transport systems were developed. Based on a Pr/T-Net model of the transportation system its current characteristics can be evaluated using the Pr/T-Net simulator. Afterwards a rule based analysis and optimization of the simulation results will take place using the Intelligent Framework Services. As further application domains for the Pr/T-Net model mechatronic systems, the formalization of distributed backplane-based simulation, and the design assistance for an integrated hardware/software co-design environment were regarded.

#### Mechatronic Systems:

One special group of system regarded were mechatronic systems consisting of digital components, physical components and control components. For these systems a common modelling technique based on extended Pr/T-Nets was further elaborated. In addition to the difference equation approach developed during the previous report period the state based representation of analogue components is supported. A major advantage of the state based approach is that it eases the coupling of different analogue components. Fur-

thermore, it is more commonly used for the description of physical and control components in mechatronic systems than difference equations. Within the report period a methodology has been developed which allows the modelling of state space representations by extended Pr/T-Nets. This methodology also provides solutions for the handling of nonlinear analogue components and for the coupling of different analogue components.

#### Simulate dialogue:

| Simulate i                   | Vet                            |

|------------------------------|--------------------------------|

| Actual Net Marking : M_1     | Actual Time : B                |

| Simulate : Start Stop Step S | 100<br>inulation Interval Ims] |

| Save Actual Net Marking M_1  |                                |

| Selected Net Marking : M_1   | Set Remove                     |

| ¢Previous M_1                | Hertanger mut eye b            |

| Next     All                 | Induced in the second          |

Figure 10: Simulation of Extended Pr/T-Nets (I)

# Net for left traffic light:

Figure 11: Simulation of Extended Pr/T-Nets (II)

27

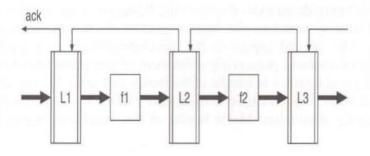

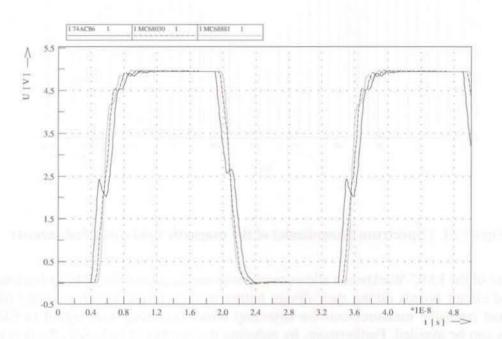

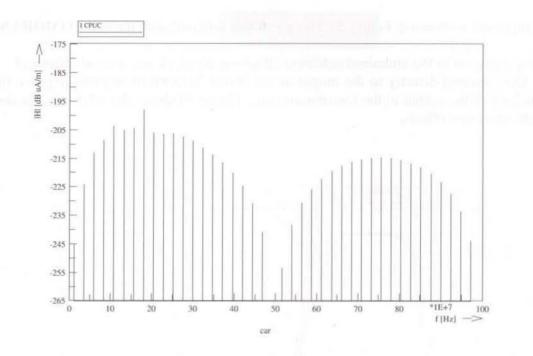

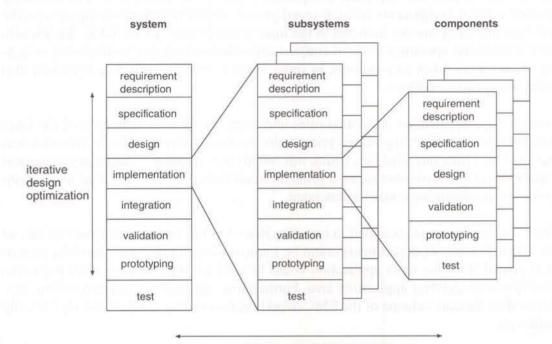

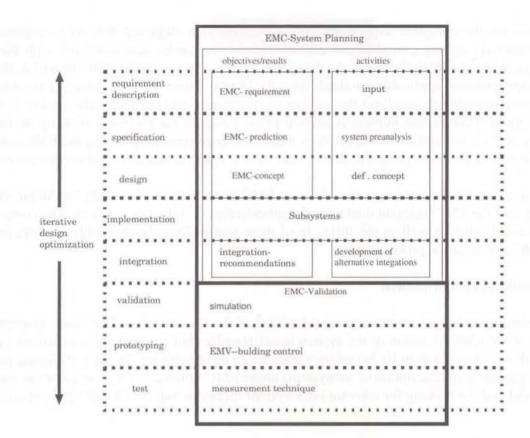

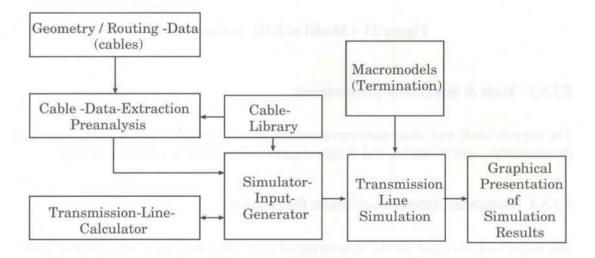

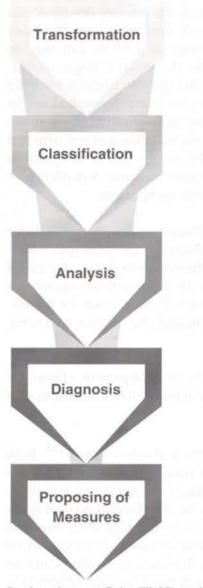

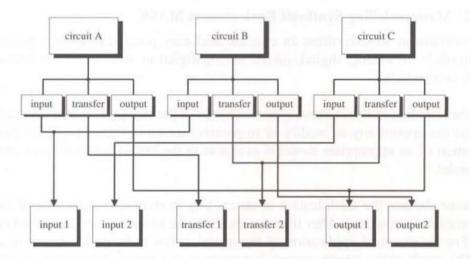

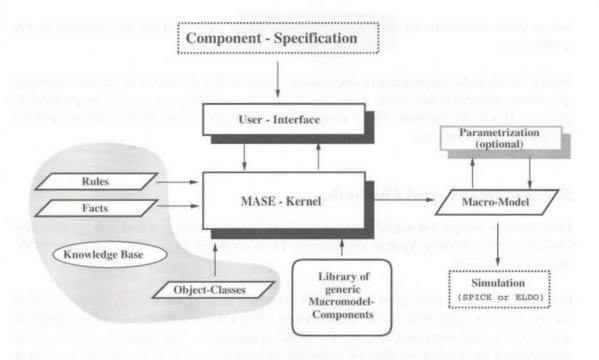

### The Formalization of Distributed Backplane-based Simulation: