### Annual Report 1993

F. J. Rammig B. Steinmüller Editors

Cadlab Report 21/94

# Cadlab Annual Report 1993

F.J. Rammig, B. Steinmüller (editors) compiled by: J. Strauß

Cadlab Bahnhofstrasse 32, D-33102 Paderborn, GERMANY

### Contents

### Preface

| Ι | Ov  | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 1   |

|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---|-----|---|-----|---|---|-----|---|---|-----|---|---|-----|

| 1 | Goa | als and Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 1   |

|   | 1.1 | Mission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 1   |

|   | 1.1 | Guiding Theme and Central Topics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 1   |

|   | 1.2 | Results and Services                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 2   |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   |     |

|   | 1.4 | Objectives of the Report Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • • | •   | • • | • | • • | • | • • | • |   | ••• | • | • | •   | • | • | 2   |

| 2 | Or  | ganization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 3   |

|   | 2.1 | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |     |     |   |     |   |     |   |   |     |   |   |     | ÷ |   | 3   |

|   | 2.2 | Advisory Board Members                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 4   |

|   |     | The answer of the second state of the second state of the second se |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   |     |

| 3 | Sun | nmary of Progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 5   |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   |     |

| п | Pr  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 7   |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   |     |

| 4 | Bas | e Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 7   |

|   | 4.1 | Baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • • | . 8 | • • | • | • • | • | . , | • | • | • • |   | ٠ | •   | • | • | 7   |

|   |     | 4.1.1 User Interface, UI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ÷,  | •   |     | • |     | • | • • |   | • | • • | • | • | ٠   | • | • | 7   |

|   |     | $4.1.2  \text{Data-oriented Integration, DI} \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |     |     |   |     |   | • • | • | • |     | • |   |     | • |   | 8   |

|   |     | 4.1.3 Control-oriented Integration, CI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | •   |     |   | • • |   |     |   | • |     | • | • | (.) |   |   | 8   |

|   | 4.2 | Work During the Report Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |     | • |     |   |     |   | • |     |   | • |     |   |   | 9   |

|   |     | 4.2.1 User Interface, UI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | •   |     | • |     | • |     | • | ٠ |     | • | • | •   | • | • | 9   |

|   |     | 4.2.2 Data-oriented Integration, DI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 12  |

|   |     | 4.2.3 Control-oriented Integration, CI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |     |     |   |     | • |     |   |   |     |   |   |     |   |   | 17  |

|   | 4.3 | Summary and Outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | •   |     | • |     | • |     |   | • |     |   |   | •   |   |   | 20  |

| - | C   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 0.0 |

| 5 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   | 23  |

|   | 5.1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   |     |

|   | 5.2 | Baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   |     |

|   | 5.3 | Work During the Report Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   |     |

|   |     | 5.3.1 System Specification and Evaluati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |     |     |   |     |   |     |   |   |     |   |   |     |   |   |     |

|   |     | 5.3.2 EXPRESS/STEP Environment .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |     |   |     |   |     |   |   |     |   |   |     | • |   | 27  |

vii

|    |     | 5.3.3   | Hardware Design Methodologies                          | 30 |

|----|-----|---------|--------------------------------------------------------|----|

|    |     | 5.3.4   | Evaluation of the JESSI-Common-Framework               | 31 |

|    |     | 5.3.5   | Simulator Generation (GRAPES-Simgen)                   | 31 |

|    | 5.4 | Summ    | nary and Outlook                                       | 32 |

| 6  | Ana | alog Sy | ystem Engineering                                      | 33 |

|    | 6.1 | Baseli  | ne                                                     | 33 |

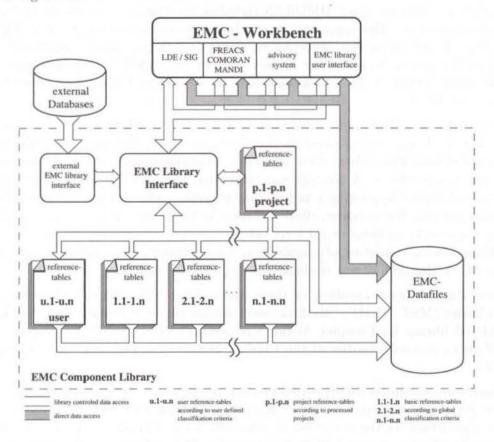

|    |     | 6.1.1   | EMC-Workbench                                          | 33 |

|    |     | 6.1.2   | Microsystem-Workbench                                  | 34 |

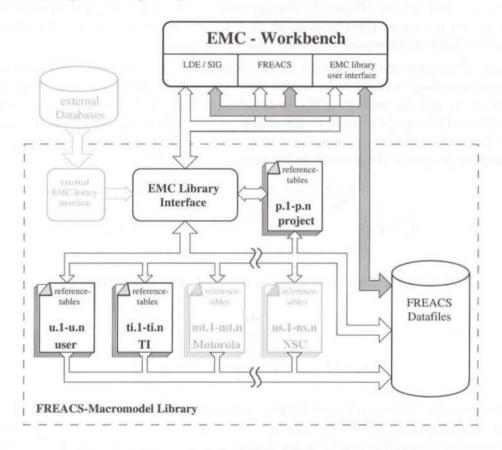

|    |     | 6.1.3   | Analog Macromodelling                                  | 34 |

|    | 6.2 | Work    | During the Report Period                               | 35 |

|    |     | 6.2.1   | EMC-Workbench                                          | 35 |

|    |     | 6.2.2   | Industrialisation of the EMC–Workbench                 | 41 |

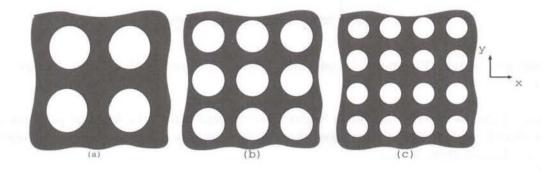

|    |     | 6.2.3   | Microsystem-Workbench                                  | 41 |

|    |     | 6.2.4   | Macro-Modelling of Analog Components                   | 42 |

|    | 6.3 | Summ    | ary and Outlook                                        | 43 |

| 7  | Tec | hnical  | Management Group and Computing Center                  | 45 |

|    | 7.1 |         | ne                                                     | 45 |

|    | 7.2 | Work    | During the Report Period                               | 45 |

|    |     | 7.2.1   | CACE Requirements Engineering                          | 45 |

|    |     | 7.2.2   | Software Engineering and Quality Assurance             | 46 |

|    |     | 7.2.3   | CADLAB Promotion and Presentation                      | 47 |

|    |     | 7.2.4   | Project Acquisition and Coordination                   | 47 |

|    |     | 7.2.5   | Computing Center                                       | 48 |

|    | 7.3 | Summ    | ary and Outlook                                        | 50 |

|    |     |         |                                                        |    |

| 11 | I P | ublica  | ations, Funded Projects, and Scientific Collaborations | 51 |

| 8  | Pub | licatio | ons and Major Documents                                | 51 |

|    | 8.1 | Cadla   | b External Reports                                     | 51 |

|    | 8.2 |         | b Internal Reports                                     | 52 |

|    | 8.3 | Major   | Software Documents                                     | 52 |

|    | 8.4 | Books   | , Conference and Journal Papers                        | 53 |

|    | 8.5 | PhD 7   | Theses                                                 | 56 |

|    | 8.6 | Maste   | rs Theses                                              | 56 |

|    | 8.7 | Extern  | nal Talks, Lectures, Tutorials, Panels                 | 56 |

|    | 8.8 | Exhibi  | itions                                                 | 56 |

| 9 | Fun | Funded Projects            |    |  |  |  |  |  |  |  |  |  |  |  |

|---|-----|----------------------------|----|--|--|--|--|--|--|--|--|--|--|--|

|   | 9.1 | Nationally Funded Projects | 57 |  |  |  |  |  |  |  |  |  |  |  |

|   | 9.2 | European Funded Projects   | 58 |  |  |  |  |  |  |  |  |  |  |  |

|   | 9.3 | Reports on Funded Projects | 59 |  |  |  |  |  |  |  |  |  |  |  |

|   |     |                            |    |  |  |  |  |  |  |  |  |  |  |  |

61

10 Collaboration in Technical-Scientific Bodies

V

## List of Figures

| 1  | Cadlab, Principal Organisational Structure                               | 3  |

|----|--------------------------------------------------------------------------|----|

| 2  | Module Structure of the Editor Framework                                 | 10 |

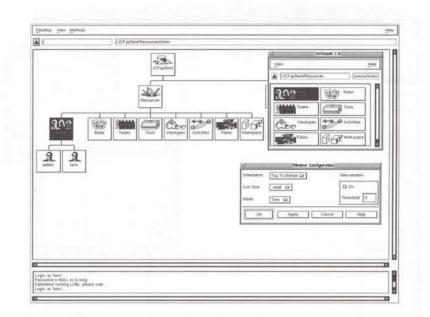

| 3  | Screen Dump of EXPREME Editor                                            |    |

| 4  | The <i>Desktop</i>                                                       | 12 |

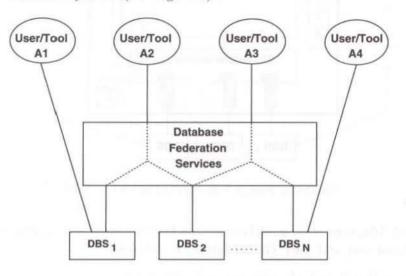

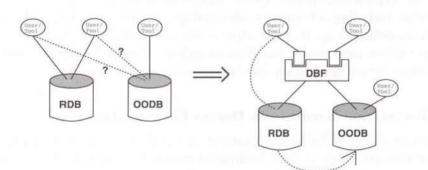

| 5  | DBF System Model                                                         | 13 |

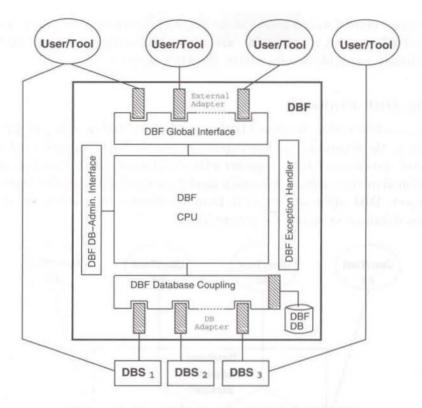

| 6  | Rough Conceptual Model of DBF                                            | 14 |

| 7  | Strong-Coupling of CDB                                                   | 15 |

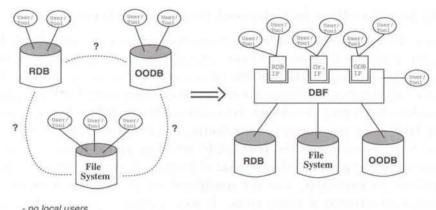

| 8  | Tool and Data Migration                                                  | 15 |

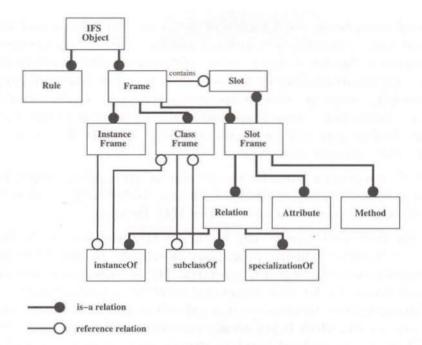

| 9  | Meta Schema for Frame Representation                                     | 19 |

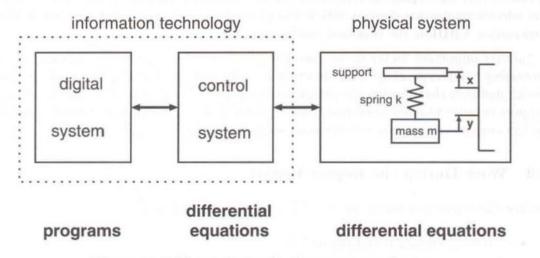

| 10 | Different Parts of a Heterogeneous System                                | 24 |

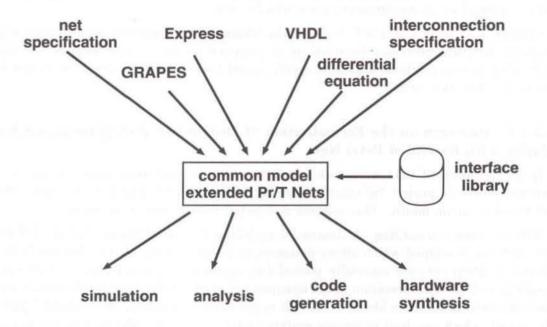

| 11 | Software Architecture for the Concurrent Design of Heterogeneous Systems | 25 |

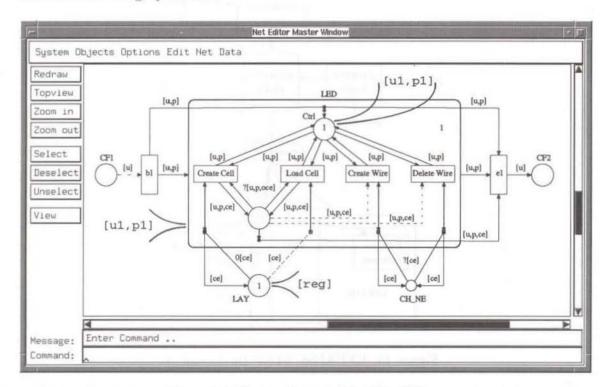

| 12 | Screen Dump of the Net Editor                                            | 27 |

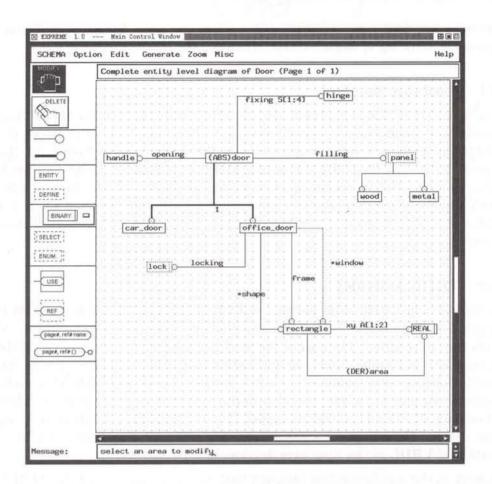

| 13 | EXPRESS/STEP Environment                                                 | 28 |

| 14 | EXPREME                                                                  | 29 |

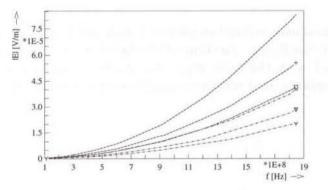

| 15 | Preliminary Structure of the EMC Component Library                       | 36 |

| 16 | Prototype of the FREACS Macro-Model Library                              | 37 |

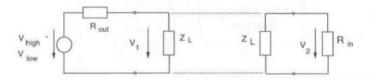

| 17 | Equivalent Circuits for Transmitters and Receivers                       | 38 |

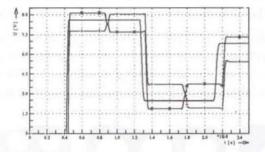

| 18 | Voltage Ringing of a Long Line Without (-) and With a Layer Change (*),  |    |

|    | (+)                                                                      | 39 |

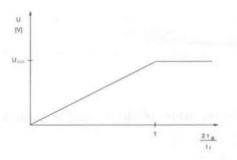

| 19 | Voltage Amplitude of the Overshoot versus $2t_d/t_r$                     | 39 |

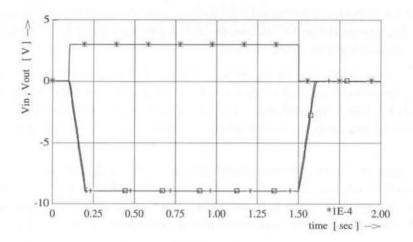

| 20 | Transient Analysis of Operational Amplifier Model                        | 44 |

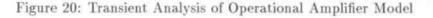

| 21 | Transient Analysis of the Comparator Model                               | 44 |

#### PREFACE

Cadlab, the joint R&D institute of Paderborn University and Siemens Nixdorf Informationssysteme AG has been founded in 1985 with the goal of deeply integrating university research and industrial development in a joint centre of excellence. In this unique cooperation scientists, although hired from both sides, work together day by day under one roof, sharing common projects, solving common problems. The Bavarian Minister for European Affaires, Dr. Thomas Goppel called Cadlab "Ein in jeder Hinsicht herausragendes, zukunftsweisendes Beispiel (an example which under any aspects is exceptional and promising)".

Cadlab's objective is to advance the field of Computer Aided Concurrent Engineering (CACE) and to provide its partners with leading edge means and methods for solving complex engineering problems. During the report period a large number of publications have demonstrated the scientific success of Cadlab while its achievements in pre-competitive product development have been demonstrated by completing Cadlab's EMC-Workbench<sup>1</sup> to a state that is ready for a demanding and fast growing market. Due to its unique organisation and a consequent path from applied research to user oriented development, Cadlab can offer today one of the most advanced solutions worldwide in this area.

From the beginning Cadlab's work has been inspired by the vision of providing smoothly integrated environments to the user in order to optimise the overall engineering process instead of isolated tools. Consequently, in the past research and development on tools always included the aspect of building integrated tool sets or "workbenches". In recent years, due to the lack of basic integration services on the market, about half of Cadlab's efforts have been spent on the conceptualisation and development of a powerful integration system or "framework". This became a major contribution to SIFRAME, SNI's framework product, which emerged from the JESSI Common Frame (JCF) project, so that today an advanced framework is on the market. As a consequence Cadlab now concentrates on integration aspects not yet covered by SIFRAME. Important examples for such aspects are the federation of existing frameworks, the support of knowledge based engineering techniques and the information exchange via standardised formats. All these efforts are necessary steps towards the successful introduction of Computer Aided Concurrent Engineering into practical applications.

At the end of the report period, about 80 scientists and engineers plus about 90 student assistants and students preparing their master's thesis were employed in Cadlab. They are organised in three groups dealing with "Base Technology", "System Engineering Technology", and "Analog System Engineering". In addition there is a "Technical Management Group".

As the results achieved will be discussed in more detail within the following sections of this report, only some highlights shall be summarised here. So called "Federated Systems", i.e., the well organised cooperation of application centred frameworks will play an important role in the introduction of Concurrent Engineering into practice. This is due to the fact that in the various engineering domains to be combined in most cases local design environments already exist and cannot simply be replaced by a completely new environment. Cadlab developed a technology to solve this problem and will be able to offer this solution in the near future. Knowledge based techniques made considerable progress

<sup>&</sup>lt;sup>1</sup>EMC: Electro-Magnetic Compatibility

in the last years. As a consequence they enter more and more all areas of engineering. A successful CACE framework therefore has to support the integration of knowledge based tools. By means of its IFS<sup>2</sup> project, started during the report period, Cadlab will offer such support. The architecture follows the proposals of the IEEE working group P1252. Advanced user interfaces become more and more the key point of any computerised application. Based on its deep knowledge in this field Cadlab started a new project in this area with the goal to design and implement an advanced, platform independent editing system. First results are operational and have been used to build applications. Concurrent Engineering means integrated engineering with heterogeneous engineering domains. While the user prefers to stay at the modelling environment he is familiar with, internally a unified modelling method has to be provided. A solution to this problem is an essential pre-requirement for successfully introducing CACE. During the report period at Cadlab a very promising approach, based on enhanced Predicate/Transition nets has been developed. The communication of data to the outside world is increasingly based on STEP protocols. To support this trend a STEP/EXPRESS workbench has been designed at Cadlab. It is highly generator-oriented and therefore extremely flexible. A first release has been finished during the report period. Cadlab's most complex software system completed in the report period is the EMC-workbench. It is one of the leading design environments worldwide to support the design of electronic systems under EMC constraints. The successful use of this software within various departments of SNI demonstrated its quality and fundamental importance. Therefore it is not surprising that there is a remarkable external market pull for this software.

The application driven research and development of Cadlab makes it necessary to participate in externally driven projects. During the report period Cadlab participated in an ambitious project on defining an innovative CAI/CACE<sup>3</sup> concept for SNI's System Unit "Midrange". This type of project is intended to become a standard Cadlab activity.

From its beginning Cadlab has been participating in large nationally and European funded projects. In 1993 two of them have been successfully finished: EMC-Design, funded by BMFT<sup>4</sup>, and ECIP II, funded by the CEU<sup>5</sup>. A couple of additional projects have been continued or newly started during the report period. This demonstrates Cadlab's reputation in the scientific and technical community.

Cadlab's standardisation efforts have been concentrated on active participation in various international bodies. Areas of Cadlab's standardisation contributions include VHDL, EXPRESS, Inter Tool Communication, Framework Architecture, Data Modelling, Simulation Backplanes, Object Oriented Databases, Engineering of Computer-based Systems.

Cadlab's international scientific reputation is reflected by the large number of publications. Cadlab employees have presented papers on most major international conferences on topics related to Cadlab's focus of research. In addition, Cadlab members have been active in organisational bodies of such conferences. Among the many outstanding scientific achievements, the international first price for graphical data processing received by R. Zhao for his work on pen-based computing deserves special recognition.

1993 was a year that demonstrated the intent and ability of Cadlab to anticipate upcoming demands and interests of Cadlab's constituting partners as well as trends and

<sup>&</sup>lt;sup>2</sup>IFS: Intelligent Framework Services

<sup>&</sup>lt;sup>3</sup>CAI: Computer Aided Industry

<sup>&</sup>lt;sup>4</sup>BMFT: Bundesministerium für Forschung und Technologie

<sup>&</sup>lt;sup>5</sup>CEU: Commission of the European Union

developments in the international research and user community. By concentrating on leading edge pre-competitive areas the workforce could be focussed on future-oriented goals. On the other hand, Cadlab has kept its proven main principles: tight integration of academic research and industrial development and focus on application oriented research and development topics.

The following annual report gives an overview of Cadlab's activities and achievements in 1993. Part I of the report details Cadlab's objectives, describes Cadlab's organisational structure and gives a general overview of the progress made. Part II contains technical details from the project groups. Part III provides supplementary information on publications, funded projects, and cooperations.

F.J. Rammig and B. Steinmüller Cadlab Executive Board Paderborn, June 1994

## Part I Overview

#### 1 Goals and Objectives

#### 1.1 Mission

Cadlab, the joint research and development institute between Paderborn University and Siemens Nixdorf Informationssysteme AG, SNI, has been founded in 1985 with the *mission* to deeply integrate university research and industrial development in a "joint centre of excellence", for the synergetic benefit of both partners.

This cooperative approach yields new possibilities for academia, namely to open-up and further new application-oriented research areas, while at the same time industry gains a sound, knowledgeable basis for developing leading-edge means and methods for mastering real-life, complex engineering problems. Last, but not least, this approach yields a very stimulating working atmosphere and a fruitful ground for the development of highly qualified application-oriented engineers and scientists.

#### 1.2 Guiding Theme and Central Topics

Cadlab's R&D work in the nineties is guided by the overall theme "Computer Aided Concurrent Engineering (CACE)".

Here, "Concurrent Engineering (CE)" stands for a systematic approach to the engineering of products, characterised by the early, concurrent consideration of all product aspects that are relevant through its further life cycle.

The key objectives of CE are

- lead time reduction

- improvement of product and environmental quality

- improvement of competitiveness

Computer Aid (CA) is seen as a pre-condition for efficiently implementing CE and for mastering CE complexity. Due to its practical importance and its academic potential, "CACE" is of high strategic interest for both partners within Cadlab.

Under this guiding theme, Cadlab focusses on the following areas of work:

- Integrated System Engineering

- Analog System Engineering

- Base Technology (CACE-Infrastructure)

These areas have been described as part of a new work programme in 1992, which has been formally issued by the Cadlab Advisory Board in the beginning of 1993.

1

#### 1.3 Results and Services

Cadlab's material results are given by

- Research and development reports in the area of CACE

- Publications and PhD theses

- Software prototypes

- Software components with industrial quality standard

Cadlab's services include

- Education and training of students and employees in application-oriented projects ("training-on-the-job")

- Coordination and support of complex R&D projects

- Execution of user projects

- User consultancy

- Transfer of know-how and software

#### 1.4 Objectives of the Report Period

While a new CACE work programme and new organisational structures have been defined in the previous report period, a major objective of the last report period was the initialisation of the work programme in the new field of base technology and integrated system engineering.

The major goal consisted in the evaluation of the relevant problem spaces, collection of user requirements and development of first prototypes and models. Moreover, a key objective was the effective take-up of leading-edge research results previously achieved by Cadlab in the areas of advanced user-interfaces, system- and data-modelling (cf. annual report 1992). In line with the idea of concurrent engineering (as applied to our own tasks) a major goal was the early assessment of potential markets and user requirements by means of close user interaction. Consequently an engineering process had to be set-up, which - while enabling adequate milestone-based process-control - was flexible enough to allow fast response to new inputs.

As for the field of "Analog System Engineering" a key goal was the industrialisation of the highly advanced computer-based workbench for Electromagnetic Compatibility EMC and its application within SNI. In particular, all necessary steps for technology transfer into a commercial context were to be taken. At the same time, new R&D areas in the analog system engineering context were to be prospected.

#### 2 Organization

#### 2.1 Overview

Cadlab is a joint venture between Paderborn University and Siemens-Nixdorf Informationssysteme AG (SNI). The financial support comes from SNI and the federal state of Nordrhein-Westfalen to about equal amounts. Additional funding is provided by the CEU and the BMFT by financing a number of research projects.

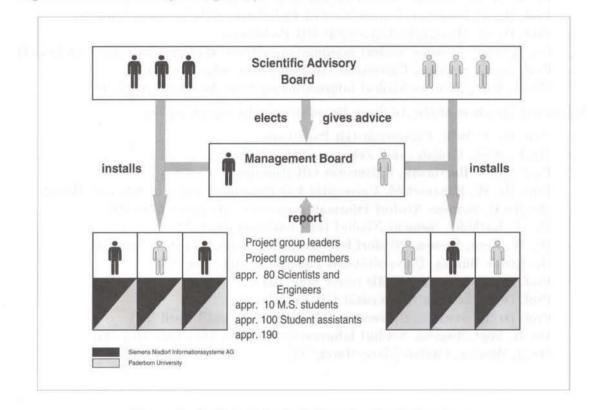

The basis of the cooperation is a contract between the two partners. The cooperation is open to further partners from academia or industry. The management of Cadlab is carried out by an executive board of two directors, one from the university and one from SNI. The executive board of directors is advised by an advisory board in technical and organisational matters (cf. Figure 1).

Figure 1: Cadlab, Principal Organisational Structure

The joint scientific and technical work is performed in project groups which are headed by project group leaders (see Fig. 1). Depending on specific needs these principle entities can be combined into larger or further sub-structured into smaller working groups. In particular, the project groups in the domains "Framework/Base Technology", "System Engineering Technology" and "Analog System Engineering" have been combined to form corresponding super project groups, which take care of the special coordination needs in these domains.

#### 2.2 Advisory Board Members

Executive Board of Directors during the report period:

Prof. Dr. F.J. Rammig, Cadlab (Universität-GH Paderborn)

Dr. B. Steinmüller, Cadlab (Siemens Nixdorf Informationssysteme AG)

Chairman of the Advisory Board:

Prof. Dr. W. Hauenschild, Universität-GH Paderborn

Members of the Advisory Board during the report period:

Mr. Heckl, Siemens Nixdorf Informationssysteme AG (until April '93)

Mr. Held, Siemens Nixdorf Informationssysteme AG (since May '93)

Prof. Dr. U. Kastens, Universität-GH Paderborn

Dr. W. Kern, Siemens Nixdorf Informationssysteme AG (since May '93)

Prof. Dr. T. Lengauer, Universität-GH Paderborn, (GMD) (until April '93)

Prof. Dr. G. Mrozynski, Universität-GH Paderborn

Dr. T. Sauer, Siemens Nixdorf Informationssysteme AG (vice chair Advisory Board)

Prof. Dr. G. Szwillus, Universität-GH Paderborn (since May '93)

Mr. H. Vogt, Siemens Nixdorf Informationssysteme AG (until April '93)

Associated Members of the Advisory Board during the report period:

Prof. Dr. F. Belli, Universität-GH Paderborn

Mr. F. Buijs, Cadlab (until February '93)

Prof. Dr. G. Hartmann, Universität-GH Paderborn

Prof. Dr. W. Hauenschild, Universität-GH Paderborn (chair of Advisory Board)

Mr. Heckl, Siemens Nixdorf Informationssysteme AG (since May '93)

Mr. T. Kathöfer, Siemens Nixdorf Informationssysteme AG

Dr. W. Kern, Siemens Nixdorf Informationssysteme AG (until April '93)

Dr. Kleine Büning, Universität-GH Paderborn (since May '93)

Prof. Dr. T. Lengauer, GMD (since May '93)

Prof. Dr. B. Monien, Universität-GH Paderborn

Prof. Dr. G. Szwillus, Universität-GH Paderborn (until April '93)

Mr. H. Vogt, Siemens Nixdorf Informationssysteme AG (since May '93)

Mr. J. Wening, Cadlab (since March '93)

#### **3** Summary of Progress

Work in the report period was driven by the mission and objectives summarised in chapter 1 above. The activities in the domain of Information Technology were largely executed in the two main groups on CACE "Base Technology (BT)" and "System Engineering Technology (SET)", while the Cadlab activities in the domain of Electrical Engineering were concentrated in the main group "Analog Systems Engineering (ASE)".

In CACE Base Technology (BT) a new research and development programme has been initialised (cf. chapter 4). This programme is directed at further extending the powerful capabilities of the JESSI Common Framework JCF/SIFRAME with new CACE services. These services are offered in a modular, portable way. Besides providing functional extensions to JCF/SIFRAME, the new CACE components can also be used outside JCF/SIFRAME. In particular, powerful facilities are offered, which support the integration and coupling between other external frameworks and CAx-Systems.

In the report period, the problem space of CACE/BT was investigated and projects on "Data Base Federation, DBF", "Advanced Editing Systems, AES", and "Intelligent Framework Services, IFS" were started. Thereby the DBF project not only treats the imminent problem of coupling heterogeneous, distributed databases, but also offers services and strategies for stepwise transforming heterogeneous systems into uniform ones by means of migration. In all projects prototypes were built and discussed with potential industrial users. These prototypes included to a large extent the results of research work performed in previous report periods. This way, a flying start could be achieved. Parallel to these development oriented activities, further applied research work was carried out in the areas mentioned as well as in "design transaction management" and "object oriented integration".

As far as the area of "System Engineering Technology SET" (see chapter 5) is concerned, the main target is the development of integrated generic environments for system development and control. In the context of CACE this includes both the "engineering of concurrent systems" and the "concurrent engineering of systems".

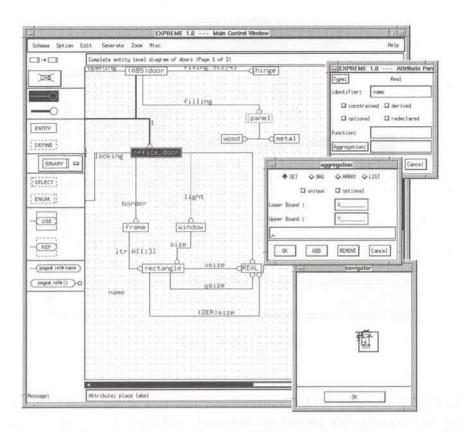

Similar to BT, a key objective in SET was the initialisation of a new R&D programme. This programme includes the exploitation of previous research results as well as the exploration of relatively new fields with a high application potential. As far as exploitation is concerned, work focussed on the industrialisation of the experience gained in the field of STEP/EXPRESS. Here, an integrated tool environment or "workbench" is under construction, which supports graphical system modelling in line with international standards. A key component of this workbench - the advanced syntax and semantic checker ICE - has already been made publicly available free of charge via the ftp server of Paderborn University. Moreover, a base version of the EXPRESS-G editor "EXPREME" for the fast, graphical design of EXPRESS models has been implemented.

Research in SET focussed on system modelling for the concurrent design of heterogeneous systems. Here a key assumption is that a CACE environment has to support different external views and models optimised for the corresponding application domain, while at the same time a common kernel model is needed to support communication between these different views. Extended timed Predicate/Transition nets were chosen as the basis for this kernel model. Research studies underlined the strengths of this approach. In particular, it could be shown how this kernel model enables the integration of digital and analog/physical aspects as for example required for the design of mechatronics systems.

The activities in the domain of "Analog System Engineering" (see chapter 6) are focussed on the development of tools and methods for the design of electronic circuits and systems under EMC-constraints. EMC stands for "Electro Magnetic Compatibility" and addresses a problem area, which has become ever more critical with the adventure of high speed electronic systems. Effective solutions in this problem area necessitate the anticipation of EMC-effects early in the design process by means of sophisticated computer aided design and analysis techniques, i.e., by adopting a CACE-approach.

In the given report period the integrated EMC-tools and techniques developed in Cadlab over the last number of years have been successfully industrialised and are now available as a product quality "EMC workbench" from Cadlab's partner SNI. Besides, library components, macro models and interfaces to different commercial CAD systems have been set-up and integrated into the workbench. The workbench is characterised by a high user orientation and practice-proveness, which has been achieved by developing the workbench in close conjunction with EMC-consultancy in SNI computer manufacturing plants. During the last report period all new SNI SINIX-computer designs have been successfully analysed and refined by Cadlab engineers using the Cadlab EMC-technology. Thus, the EMC-workbench has been successfully used and beta-tested in a highly demanding, practical production environment.

Apart from the development of new components, the extension of the EMC-CACE approach to new application domains has been undertaken. A generic design process model has been constructed and implemented. This model now can be customised to optimally suite particular application requirements. Special consideration has been given to the domain of micro-systems, which currently is positioning itself as one of the promising key technologies in Europe's industrial future.

Efficient support for the ongoing R&D work was provided by the Cadlab "Technical Management Group, TMG" and the "Computing Centre, CC" (cf. chapter 7). Thereby TMG also provided internal and external CACE-consultancy. This way know-how transfer was effectively supported, while at the same time new ideas and requirements for Cadlab's future work were collected. Last, but not least, TMG was active in project support and acquisition for Cadlab as well as for Cadlab's partners. The Cadlab Computing Centre, CC, efficiently maintained a complex network environment with more than one hundred workstations and twenty PCs. CC also continued to support a closely related SNI unit, which formerly belonged to Cadlab.

Most of Cadlab's work was carried out in the context of collaborative projects (see chapter 9). Concerning nationally funded collaborations, Cadlab has participated in eight BMFT projects, two of them executed in the frame of the European JESSI programme. Thereby, the large European EMC project JESSI AC-5 is also led by Cadlab. Three more projects are funded by ESPRIT, one of them being the JESSI project AC-1 on frameworks, which Cadlab has successfully managed during the last reporting periods.

Publications and dissemination of technical/scientific results again played a major role also in this report period (see chapters 8–10). A number of master theses were completed under the supervision of Cadlab employees. Among the many outstanding scientific achievements, the international first price for graphical data processing received by R. Zhao for his work on pen-based computing deserves special recognition.

## Part II Project Group Reports

#### 4 Base Technology

#### 4.1 Baseline

The project group "Base Technology" was formed in October 1992 with the mission to investigate infrastructures needed for CACE and to provide basic services for building CACE environments. These services should be offered as flexible software building blocks, such as to be useful in a wide range of practical environments. In particular, smooth inter-operability with  $JCF/SIFRAME^{TM6}$  is planned.

Among the CACE-services to be built, the following ones should be emphasised in the beginning:

- Innovative interaction and presentation services

- Federation services for heterogeneous, distributed systems

- Framework services for knowledge-based techniques

Accordingly, the tasks of base technology are executed in three subgroups: UI (User Interface), DI (Data-oriented Integration), CI (Control-oriented Integration). The baselines for these groups and the work performed during the report period are detailed below.

#### 4.1.1 User Interface, UI

At the beginning of 1993, two research prototypes were completed as the results of two PhD theses within this project group. The first one is called Handi (Hand-sketch-based Diagram Editing), the name of the second one is Edis (Editor Description and Implementation System).

Edis provides a concept to separate dialogue control of graphical editors from presentation. Instead of call-backs and event-handlers, non-blocking input requests are used to couple presentation and dialogue control. This allows an abstract description of the end-user's commands, without loosing features like direct manipulation and semantical feedbacks.

Handi is a framework for building hand-sketch-based diagram editors and has been designed for reducing the efforts required by building gesture-based diagram editors. It provides concepts and mechanisms for on-line recognising hand-sketches and for specifying gestures as editing commands. The basic idea of Handi is to encapsulate common characteristics of hand-sketch-based diagram editors into classes by using an object-oriented methodology. Handi specialises basic abstractions of general editor frameworks for directly supporting common features of diagram editors.

<sup>&</sup>lt;sup>6</sup>Siemens Nixdorf Informationssysteme AG, SIFRAME Product Sheet, 1993.

In order to transfer these practically relevant research results into industrial re-usable products, the project AES (Advanced Editing Systems) was initiated. One of the most important goals of the AES project has been to transfer the research results into products. Furthermore, there is much internal and external need to support the development of graphical editors. Under these considerations, the project has two aspects: The first aspect is to transfer the research results into a product, in form of an editor framework; the second one is to develop application-specific graphical editors.

#### 4.1.2 Data-oriented Integration, DI

Within Cadlab, the project group "Data-oriented Integration, DI" covers the field of object-oriented database technology and its applications. In former years work in this field was focussed on research and development of components for a single object-oriented database system. For example, development of components for JCF/SIFRAME data handling system was supported.

Investigating data handling facilities within CACE environments has shown, that new requirements have to be fulfilled. In particular, the user and system communities must have autonomous access as well as uniform global access to already existing and new data repositories. Here, data repositories are represented by file systems and database systems of different technologies.

Due to these requirements focus of the project group DI is the development of "Database Federation Services, DBF". The aim of this work is the federation of homogeneous resp. heterogeneous, autonomous databases. Here, federation and coupling of object-oriented database systems together with database systems based on the relational model or the entity-relationship-model is of interest. The "Database Federation Services" offer a solution in form of a logical, homogeneous software layer on top of the homogeneous resp. heterogeneous databases to be federated. This software layer can be used as a "standalone" component as well as an integrated component of JCF/SIFRAME.

To enable the tasks of the DBF project several fundamental components from the field of database technology have to be developed. For example, graphical editors for defining database schemas, data dictionaries for storing and retrieving information about the federated database systems, and database interfaces for defining, manipulating and querying data within the federated system were developed. Database interfaces need to be developed under consideration of current resp. upcoming standards in database technology, for example SQL-2 and Object Database Management Group (ODMG).

#### 4.1.3 Control-oriented Integration, CI

In the past years considerable progress has been made in research and development of knowledge based systems as well as knowledge base infrastructure, which is called "shell" in this context. Nevertheless, these systems have not been as successful as expected some years ago. One of the identified reasons is the lack of integration facilities of these usually stand-alone systems. Therefore, a key requirement is to provide a comprehensive methodology for the development of knowledge based systems, and to integrate and maintain intelligent services in JCF, which utilise these techniques.

To enable this task the project *Intelligent Framework Services* (IFS) was started in March 1993. The goal of this project is to provide an infrastructure to support the development of tools which use declarative knowledge to perform intelligent behaviour, and which can be deeply integrated within a CACE environment. The second requirement posed on IFS is to follow the toolbox approach, thus permitting to use only those modules of knowledge based services which are required to fulfil the task of a certain tool.

Knowledge representation is one of the central design problems. For the hybrid knowledge description language HyKL therefore a combination of frame-based representation mechanism with rule-based reasoning needs to be employed.

For the development of the frame-part of HyKL, a proposed IEEE standard is used as a base. This *Standard for a Frame-Based Knowledge Representation* is developed by the IEEE working group P1252.

#### 4.2 Work During the Report Period

#### 4.2.1 User Interface, UI

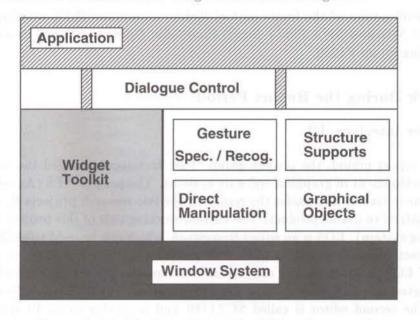

Within the report period, the project group "User Interface" changed the focus from research to development of graphical software systems. The project AES (Advanced Editing Systems) was initiated, to transfer the results of the two research projects Handi and Edis into an industrial re-usable product. The current working title of this project is EOS (Editor operating system). EOS is an editor framework, which can be used to easily implement highly interactive applications, in particular graphical editors. In order to evaluate the concepts of EOS in practice, the concurrent development of two EOS-based editors has been supported and supervised. The first editor is an EXPRESS-G editor called EX-PREME. The second editor is called SCALOR and is similar to an PCB layout editor with additional features required by the EMC Workbench.

Besides the AES project, support for the desktop application of SIFRAME 3.0 has been an important activity.

#### 4.2.1.1 Project Advanced Editing Systems (AES)

The project AES was initiated in February 1993 and was managed by following the SNI Process Technology with Cadlab adaptations. Within the SNI Process Technology, a project has to pass several project master process steps. Within the report period, the AES project completed the first master step, the "Problem Analysis", the second master step, the "Product Definition", was started and is in progress at the moment.